Czego można się nauczyć z tego artykułu

Przyznajmy – to bardzo obszerny artykuł. Jednak jego zakres wykracza daleko poza samą pętlę PLL. Poznasz kilka bardzo ważnych zagadnień z elektroniki analogowej, takich jak detektory fazy, oscylatory sterowane napięciem (VCO) oraz zasady działania sprzężeń zwrotnych pomiędzy poszczególnymi blokami. Omawiane elementy składowe pętli synchronizacji fazowej spotyka się nie tylko w tego typu układach, ale również jako samodzielne, praktyczne rozwiązania.

Podstawowa zasada działania PLL

Dosłowne tłumaczenie skrótu PLL (Phase-Locked Loop) to pętla synchronizacji fazowej. Taka pętla umożliwia zsynchronizowanie częstotliwości lub fazy dwóch sygnałów zmiennych. Oznacza to, że układ automatycznie dostosowuje częstotliwość lub fazę drugiego sygnału do odpowiednich parametrów sygnału odniesienia.

Schemat blokowy PLL

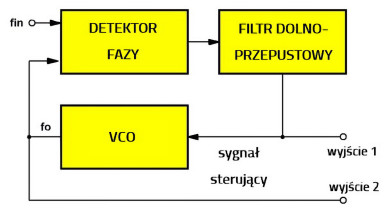

Schemat blokowy pętli PLL przedstawiono na poniższym rysunku. Sercem układu jest VCO, czyli oscylator sterowany napięciem. Generuje on sygnał wyjściowy fo, którego częstotliwość jest określana przez napięcie sterujące doprowadzone do wejścia VCO.

Sygnał wyjściowy z tego oscylatora jest porównywany w tzw. detektorze fazy z fazą i częstotliwością sygnału wejściowego PLL. Detektor ten wytwarza napięcie stałe, którego wartość i biegunowość są proporcjonalne do różnicy częstotliwości lub fazy obu sygnałów wejściowych.

W większości przypadków sygnał wyjściowy detektora fazy ma jednak postać przebiegu impulsowego i nie nadaje się bezpośrednio do sterowania VCO, który wymaga napięcia stałego. Dlatego pomiędzy tymi blokami stosuje się filtr dolnoprzepustowy, który przekształca sygnał impulsowy z wyjścia detektora fazy w wygładzone napięcie stałe. To właśnie to napięcie steruje częstotliwością oscylatora VCO.

Rola sprzężenia zwrotnego w pętli PLL

Pętla PLL jest układem ze sprzężeniem zwrotnym, w którym sprzężenie powoduje, że każda zmiana fazy lub częstotliwości sygnału wejściowego jest natychmiast przekazywana do generatora VCO. Generator ten możliwie szybko dostosowuje własną częstotliwość lub fazę, przywracając zgodność obu wielkości.

Podstawowy schemat układu PLL

Jak już wspomniano, najprostsza pętla PLL składa się z trzech bloków:

- detektora fazy na wejściu,

- filtru dolnoprzepustowego,

- generatora sterowanego napięciem (VCO).

Bloki te są połączone w sposób przedstawiony na rysunku powyżej. Taki układ stanowi podstawę każdej pętli PLL i występuje niezależnie od stopnia złożoności konkretnego rozwiązania.

W kolejnych rozdziałach najpierw omówione zostanie działanie poszczególnych bloków, a następnie ich współpraca w układzie ze sprzężeniem zwrotnym. To właśnie sprzężenie zwrotne nadaje pętli PLL jej unikalne właściwości.

Detektor fazy

Trzy techniki

Do realizacji detektora fazy stosuje się różne rozwiązania. Najczęściej spotykane są trzy:

- bramka EXOR (XOR),

- detektor fazy sterowany zboczami (edge-controlled),

- mnożnik analogowy.