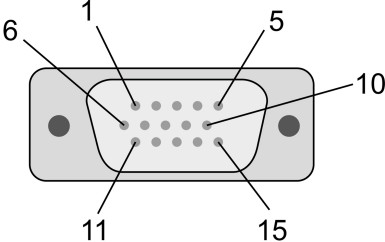

Zacznijmy od omówienia sygnałów, jakie znajdują się w 15-pinowym konektorze D-Sub, używanym w interfejsie VGA. Zarówno monitor, jak i generator obrazu (tzn. karta graficzna komputera lub dowolne inne urządzenie dostarczające obrazy graficzne) wyposażone są w złącze żeńskie, a po obu stronach kabla powinny znajdować się wtyczki w wersji męskiej.

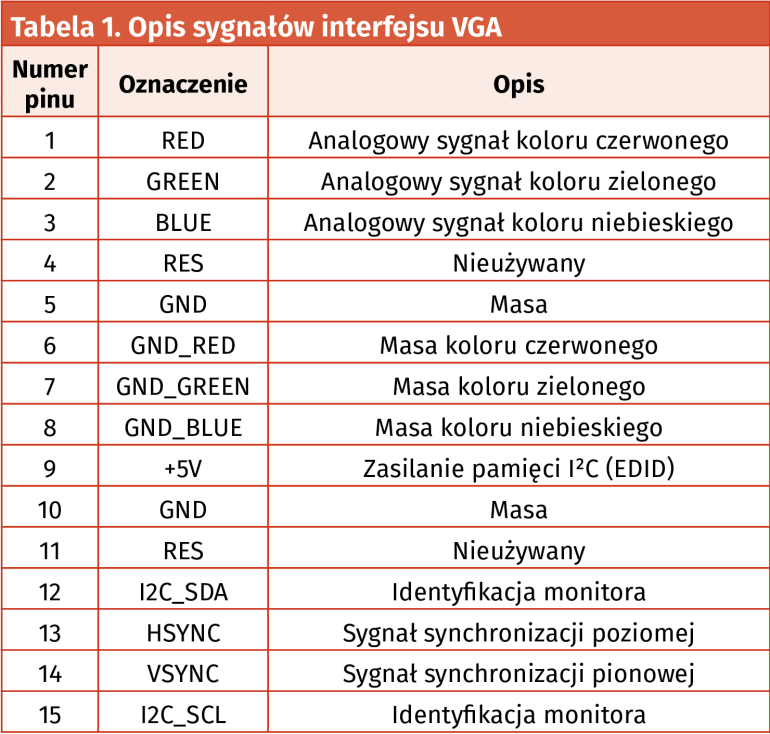

Układ wyprowadzeń złącza pokazano na rysunku 1, a opis sygnałów zamieszczono w tabeli 1.

Linie te możemy podzielić na trzy grupy: sygnały analogowe odpowiedzialne za generowanie obrazu (piny 1, 2, 3, 13, 14), cyfrowa szyna danych służąca do identyfikacji monitora i jego możliwości oraz różne masy, które w praktyce można połączyć razem ze sobą.

Na przestrzeni lat zmieniały się standardy identyfikacji monitorów. W latach 90. wprowadzono standard EDID, bazujący na danych zapisanych w prostej pamięci EEPROM typu 24C z interfejsem I²C, która znajduje się wewnątrz monitora. Linie danych pamięci, tzn. SDA i SCL, wyprowadzone są wprost na złącze VGA. Pamięć ta działa nawet wtedy, gdy monitor nie jest podłączony do zasilania – w takiej sytuacji pamięć zasila się z komputera za pośrednictwem pinu 9, który dostarcza napięcie 5 V. Aby odczytać dane z pamięci, musimy wywołać ją na magistrali I²C spod adresu 0x50, a dalej postępować tak samo, jak w przypadku zwyczajnych pamięci szeregowych. W ten sposób można odczytać informacje o modelu monitora, producencie, obsługiwanych rozdzielczościach, kolorach, częstotliwości odświeżania obrazu, itp.

Warto dodać, że w taki sam sposób rozpoznawane są monitory ze złączami DVI i HDMI. W tym odcinku kursu nie będziemy jednak szczegółowo omawiać tego tematu.

Piny 1, 2, 3 dostarczają informacje na temat składowych kolorystycznych: czerwonej, zielonej i niebieskiej aktualnie wyświetlanego piksela. Są to sterowane napięciowo wejścia analogowe. Zakres dopuszczalnych napięć może zmieniać od 0 do 0,7 V – im wyższe napięcie, tym jaśniejszy kolor piksela. Każde z tych wejść połączone jest do masy poprzez rezystor 75 Ω. Nasz układ FPGA pracuje przy napięciu 3,3 V, zatem pomiędzy nim a wyjściem VGA musimy umieścić dodatkowe rezystory, które wraz z rezystorami wewnątrz monitora będą tworzyć dzielnik napięcia. Z tego powodu na płytce User Interface Board zastosowano rezystory 270 Ω. Dzielnik napięcia zasilany z 3,3 V, składający się z rezystorów 270 Ω i 75 Ω, da bowiem na wyjściu napięcie 0,7 V. Proste i skuteczne.

Sygnały HSYNC i VSYNC służą do synchronizacji monitora z urządzeniem nadającym sygnał. Sposób synchronizacji jest bardzo staroświecki i wynika ze sposobu działania lamp elektronopromieniowych, zwanych w skrócie CRT. Budowę takiej lampy pokazano na rysunku 2.

Składa się ona z działa elektronowego, które emituje wiązkę elektronów oraz z ekranu pokrytego luminoforem. Warstwa luminoforu świeci tym jaśniej, im więcej elektronów ją bombarduje. Ruchem elektronów sterują dwie pary elektrod kierujących, które – w zależności od przyłożonego napięcia – mogą wiązkę elektronów odchylać pionowo i poziomo. W ten sposób wiązka przemiata cały ekran, linia po linii, zaczynając od lewego górnego rogu i kończąc na prawym dolnym.

Sygnał synchronizacji pionowej mówi nam, że właśnie rozpoczyna się transmisja nowej klatki obrazu, a sygnał synchronizacji poziomej oznacza początek każdej kolejnej linii. Sygnały te nazywane są sync pulse. Jednak elektrody odchylania poziomego i pionowego potrzebują trochę czasu, aby cofnąć wiązkę na pozycję początkową, czyli przeładować napięcie, jakie na nich występuje. Z tego powodu potrzebujemy dodatkowych dwóch faz cyklu, nazywanych front porch i back porch. W tym czasie obraz nie jest wyświetlany, a układ sterujący lampą CRT wytwarza odpowiednie napięcia, potrzebne do wyświetlenia kolejnej linii od początku.

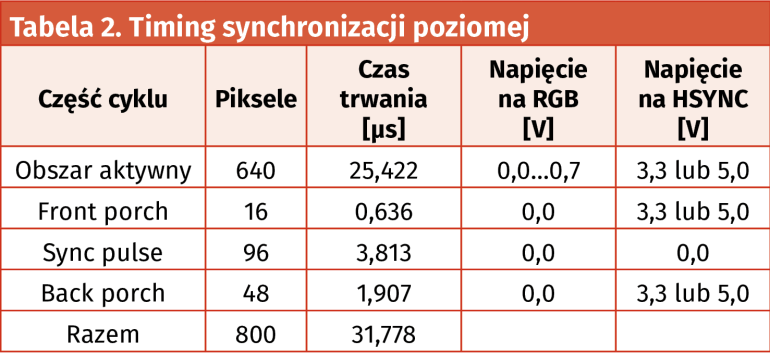

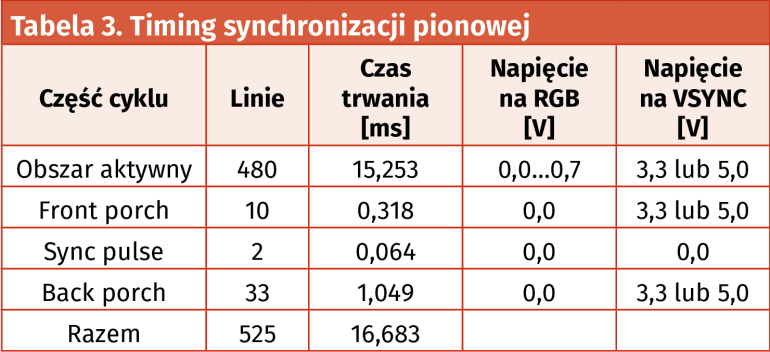

W tabelach 2 i 3 zebrano czasy wszystkich czterech części cyklu pionowego i poziomego, obliczone dla rozdzielczości 640×480 pikseli i odświeżania 60 Hz. Jeżeli czas ten przeliczymy na piksele, wówczas okazuje się, że do monitora musimy dostarczyć obraz o rozdzielczości 800×525 pikseli. W tym nadmiarowym czasie sygnały odpowiedzialne za kolory czerwony, zielony i niebieski mają napięcie równe 0 V, a pracują jedynie linie synchronizacji pionowej i poziomej.

Policzmy pewną rzecz. Jeżeli zgodnie z tabelą 2 mamy wyświetlić 640 pikseli w czasie 25,422 μs, to czas wyświetlania jednego piksela powinien wynosić 39,722 ns. Jeżeli obliczymy odwrotność wyniku, to uzyskamy 25,175 MHz. Jest to częstotliwość, jaką najwygodniej będzie taktować układ FPGA, aby każdy takt zegarowy odpowiadał za wyświetlanie jednego piksela. Na szczęście monitory są tolerancyjne i dopuszczają dość duże odchyłki w częstotliwości taktowania sygnałów, zatem bez problemu można zastosować zegar o częstotliwości 25 MHz, bo jest popularniejszy i łatwiej dostępny.

![Rysunek 2. Budowa lampy elektronopromieniowej w monitorze kineskopowym [3]](/i/2025/01/16/22538-d561-770x0_r2-kurs-fpga27.jpg)