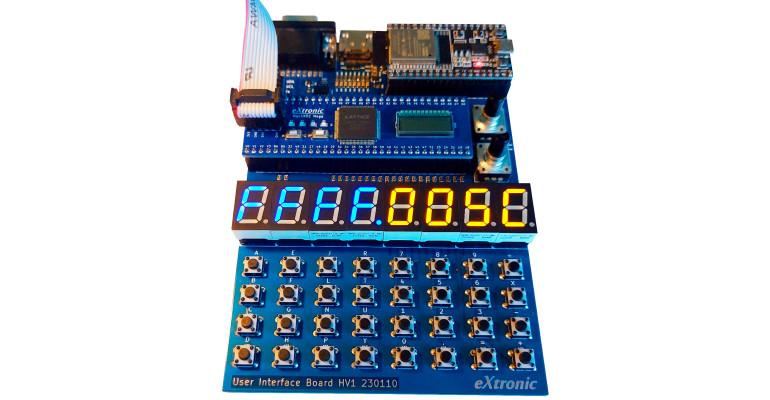

Enkoder obrotowy składa się z pokrętła i opcjonalnie w tym pokrętle może być także przycisk. Na płytce User Interface Board zastosowano enkodery typu EC12E20-24P24C-SW firmy SR Passives.

Enkoder tego typu ma dwa wyjścia, dzięki którym możemy odczytać informacje o obrocie pokrętła. Są to wyjścia A i B, dostępne na pinach 1 i 3. Wyjście S, dostępne na pinie 4, informuje o wciśnięciu pokrętła. Wewnątrz enkodera znajduje się mechanizm zwierający wyjścia A, B i S z pinami 2 i 5, które najwygodniej jest podłączyć prosto do masy.

Wyjście S działa jak zwyczajny przycisk. Kiedy pokrętło enkodera jest wciśnięte, wówczas pin numer 4 jest połączony z masą, co powoduje, że sygnał Enc1-S przechodzi w stan niski. Jednak kiedy pokrętło nie jest wciśnięte, to stan wysoki jest wymuszany przez rezystor pull-up R42.

Wyjścia A i B również mają możliwość zwierania do masy i należy zastosować rezystory pull-up R40 i R41. Wyjścia te są naprzemiennie zwierane do masy przez mechanizm enkodera, w zależności od kierunku obrotu – o tym będzie kilka akapitów niżej.

Pary rezystorów i kondensatorów R43-C40, R44-C41 oraz R45-C42 tworzą filtr dolnoprzepustowy, którego zadaniem jest odfiltrowanie drgań styków. W ten sposób powstaje sygnał wolnozmienny, który powoli narasta lub opada, w miarę ładowania i rozładowywania kondensatora C40, C41 lub C42. Pamiętać należy, że takie sygnały nie powinny być doprowadzone wprost do zwykłego wejścia cyfrowego, ponieważ mogą powodować wielokrotne zmiany stanu, czyli mielibyśmy wciąż ten sam problem, co drgania styków. Rozwiązaniem jest zastosowanie wejść z histerezą. Tak się składa, że wszystkie piny w FPGA MachXO2 są wyposażone w przerzutnik Schmitta z histerezą – wystarczy ją tylko uaktywnić w narzędziu Spreadsheet.

Jeżeli jednak zależy nam, by ciąć koszty elementów, a mamy wolne zasoby w FPGA, to w takiej sytuacji można by ze schematu 1 usunąć wszystkie rezystory i kondensatory. Wtedy drgania styków trzeba odfiltrować w FPGA, na przykład implementując moduł Debouncer, który omawialiśmy w 6 odcinku kursu.

Przyjrzyjmy się bliżej sygnałom A i B. Kiedy nic się nie dzieje, oba sygnały pozostają w stanie wysokim. Enkoder typu EC12E20-24P24C-SW podczas obrotu wytwarza kliknięcia, które użytkownik wyczuwa palcami jako potwierdzenie, że enkoder zarejestrował obrót. Kliknięcie występuje po obrocie pokrętła co każde 15°. Pełny obrót to 24 kliknięcia.

Podczas każdego kliknięcia następują cztery zmiany sygnałów A oraz B. Zobacz rysunek 2. Jeżeli kręcimy w prawo, to najpierw sygnał A przechodzi w stan niski, natomiast jeżeli kręcimy w lewo, to najpierw zbocze opadające zaobserwujemy na sygnale B. W ten sposób możemy określić kierunek obrotu.

Należy podkreślić, że istnieją enkodery, które nie klikają podczas obracania i mają inną liczbę impulsów na obrót. Ponadto w enkoderach bez klikania nie da się wyróżnić stanu spoczynkowego, bo sekwencja zmian sygnałów A i B może być zatrzymana w dowolnym momencie.

Jednak zanim zaczniemy analizować zmiany sygnałów A, B i S, to musimy z nimi coś zrobić, aby przypadkiem nie wpaść w pułapkę metastabilności. Co takiego? Sygnały z enkodera doprowadzone do pinów FPGA to sygnały całkowicie asynchroniczne, zmieniające się w sposób niezależny od sygnału zegarowego, więc mogłyby spowodować błąd setup time lub hold time. Musimy je zsynchronizować z sygnałem zegarowym, który taktuje pozostałe elementy wewnątrz FPGA.

Jeżeli nie wiesz dlaczego – koniecznie przeczytaj 11 odcinek kursu.

W tym celu najpierw musimy zbudować moduł synchronizujący.