Wszyscy więksi producenci udostępniają narzędzia do analizowania sygnałów wewnątrz FPGA, które działają dość podobnie. Xilinx udostępnia narzędzie ChipScope, Intel oferuje Signal Tap, a Lattice daje nam Reveal. Jest to narzędzie bezpłatne i zintegrowane z pakietem Diamond, którego możemy używać bez żadnych dodatkowych licencji czy ograniczeń.

Idea działania analizatora jest bardzo prosta. Za pomocą programu Reveal Inserter tworzymy moduł analizatora, który łączymy z interesującymi nas sygnałami. Moduł ten jest w istocie zwyczajnym modułem sporządzonym w języku Verilog. Mamy nawet dostęp do jego plików źródłowych, chociaż ich ręczna edycja jest niepotrzebna. Wszystko możemy skonfigurować za pomocą interfejsu graficznego.

Następnie, mając już utworzony moduł analizatora, dokonujemy syntezy, mapowania, generujemy bitstream i wgrywamy go do FPGA. Aby odczytywać dane z analizatora, wykorzystamy narzędzie Reveal Analyzer, które łączy się z analizatorem poprzez port JTAG - ten sam, który wykorzystywany jest przez programator. Dzięki takiemu rozwiązaniu nie potrzebujemy modyfikować projektu płytki, na której pracuje nasz układ FPGA.

Analizator i symulator to dwa narzędzia, które pomogą nam debugować kod. Każdy z nich ma swoje wady i zalety, dzięki czemu te narzędzia dobrze się uzupełniają. Największą zaletą analizatora jest to, że bada sygnały rzeczywiste, które faktycznie występują w badanym układzie FPGA. Jeżeli wyniki analizatora i symulatora nie zgadzają się ze sobą, to znaczy, że nie uwzględniliśmy czegoś w symulacji. Ponadto, analizator jest niezwykle przydatny, kiedy debugujemy komunikację FPGA z jakimiś innymi układami scalonymi. Symulowanie układów scalonych, które przesyłają dane do FPGA, jest dość trudne i czasochłonne.

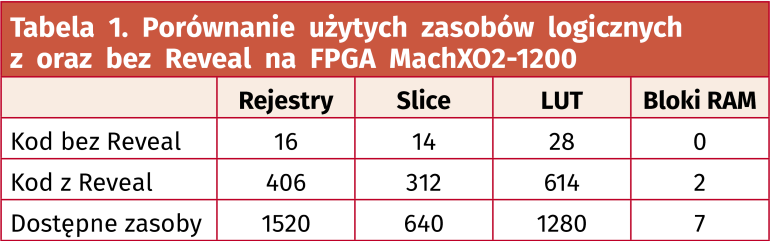

Analizator ma jednak swoje wady. Musimy przeznaczyć sporo zasobów logicznych, aby analizator mógł w ogóle zacząć pracę. Może się okazać, że nasz design z doklejonym analizatorem nie zmieści się do FPGA. Nie ma możliwości, by Reveal zastosować w najmniejszych maluchach - układy MachXO2-256 oraz MachXO2-640 nie mają wystarczających zasobów, by mógł on działać. Obecność analizatora może także zmniejszyć maksymalną dopuszczalną częstotliwość zegara i wydłużyć czas propagacji sygnałów. Symulacja wygrywa pod tym względem - symulator nie potrzebuje żadnych zasobów w FPGA, ponieważ działa w całości na komputerze.

W tabeli 1 porównano, ile zasobów potrzebnych jest, aby zrealizować projekt z tego odcinka kursu w FPGA MachXO2-1200. Zasoby potrzebne na analizator Reveal mogą zmieniać się w bardzo szerokim zakresie. Zależą od liczby badanych sygnałów, wyzwalaczy oraz liczby próbek, jaka ma zostać zbadana i zapisana w pamięci.

Kolejną wadą jest konieczność ponownej syntezy i wgrywania bitstreamu do FPGA, kiedy zmieniamy konfigurację obserwowanych sygnałów i wyzwalaczy. Może to być czasochłonne, ale przy odrobinie wprawy można nauczyć się tak tworzyć analizatory, by spełniały oczekiwania już przy pierwszej próbie.

W tym odcinku użyjemy kodu, który opracowaliśmy w kwietniowym wydaniu EP. Kod całego projektu wraz z analizatorem jest dostępny w materiałach dodatkowych do artykułu. Jeżeli nie czytałeś poprzedniego odcinka, przeczytaj go koniecznie, ponieważ dalsza część tekstu będzie niezrozumiała.