W tej części kursu będzie dużo teorii. Problemy, jakie będziemy dzisiaj poruszać, są niezwykle ważne, a wręcz fundamentalne. Brak znajomości tych zagadnień może prowadzić do bardzo irytujących błędów, które mogą być bardzo trudne do wykrycia i naprawienia. Jednak bądź dobrej myśli! Niedługo stwierdzisz, że to wcale nie jest takie trudne i nauczysz się zręcznie omijać pułapki.

Glitch

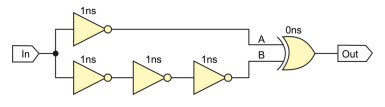

Zacznijmy od prostego eksperymentu, który uświadomi nam pewien problem, którym obarczony jest każdy układ kombinacyjny. Zastanówmy się nad banalnym schematem, który pokazano na rysunku 1.

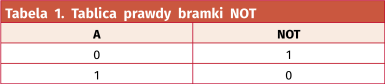

Na schemacie są tylko cztery bramki NOT i jedna bramka XOR. Ich tablice prawdy dla przypomnienia pokazano w tabelach 1 i 2. Układ ma tylko jedno wejście, oznaczone jako In oraz jedno wyjście Out.

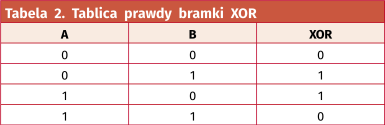

Spróbujmy teraz stworzyć tablicę prawdy dla całego układu. Jest tylko jedno wejście, które może przyjmować tan 1 lub 0, więc musimy przeanalizować tylko dwie możliwości, jakie mogą wystąpić na wejściu In. W tablicy uwzględnimy także punkty pośrednie A i B, które są wejściami bramki XOR. Wynik tej symulacji zaprezentowano w tabeli 3. Okazuje się, że obojętnie jaki stan jest doprowadzony do wejścia In, to na wyjściu Out zawsze jest stan niski.

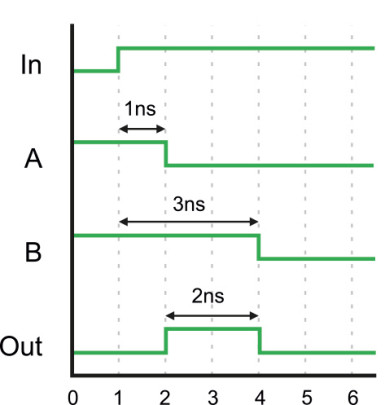

W naszej prostej symulacji nie uwzględniliśmy bardzo ważnego czynnika – czasu propagacji. Jest to czas, jaki mija pomiędzy ustaleniem się stanu na wejściu układu, a ustaleniem się stanu jego wyjścia. Załóżmy, że bramki NOT mają czas propagacji równy 1 nanosekundzie, a bramka XOR niech ma zerowy czas propagacji (dla wygody) – czasy propagacji bramek podano na rysunku 1 nad symbolami bramek. Aby przeprowadzić symulację czasową, już nie wystarczy prosta tabelka. Potrzebujemy wykres, jaki znajduje się na rysunku 2. Naszą sekwencją testową, którą byśmy umieścili w testbenchu pisząc kod w Verilogu, niech będzie jedynie przełączenie się sygnału In ze stanu 0 na 1, a następnie niech ten sygnał pozostaje bez zmian, aż do końca symulacji.

Sprawdźmy, co będzie działo się w punkcie A. Sygnał przechodzi przez jedną bramkę NOT, więc zostanie zanegowany. Jednak ta bramka ma czas propagacji 1 ns, więc efekt negacji zobaczymy po upływie 1 ns. W punkcie B mamy podobną sytuację, lecz sygnał musi przejść przez trzy bramki NOT, więc stan tego punktu ustali się po upływie 3 ns. Co się dzieje wtedy z bramką XOR? Zwróć uwagę, że przez czas 2 nanosekund na wejściu A jest stan niski, a na wejściu B jest stan wysoki. Zgodnie z tabelą 2, w takiej sytuacji wyjście bramki XOR powinno ustawić się w stan wysoki! Dopiero, kiedy łańcuch bramek NOT przetworzy zmianę sygnału, to na obu wejściach A i B ustali się stan niski. Wyjście bramki XOR przełączy się ponownie w stan niski po upływie 3 ns od zmiany stanu wejścia In (gdybyśmy chcieli uwzględnić czas propagacji bramki XOR, wtedy wykres Out należałoby przesunąć w prawo o czas propagacji tej bramki).

Okazuje się, że przez czas dwóch nanosekund wyjście na wyjściu układu jest krótka szpilka, której nie powinno być. Jest to tzw. glitch. Ta krótka szpileczka może powodować bardzo poważne problemy. Gdybyśmy odczytali wyjście Out, zanim ustali się jego stan, to byśmy otrzymali nieprawidłową wartość tego sygnału. Ten nieprawidłowy stan przedostałby się do dalszych bramek, przerzutników, multiplekserów, przez co nasze urządzenie działało by w sposób nieprawidłowy!

Glitch jest zjawiskiem występującym w układach kombinacyjnych. Im bardziej skomplikowany układ, tym więcej ścieżek jest do przeanalizowania i tym więcej różnych glitchy może powstać. W naszym prostym układzie mamy tylko dwie ścieżki. Jak ten problem rozwiązać? Z pomocą przychodzi przerzutnik D.