Opis ukŇāadu i jego dziaŇāanie

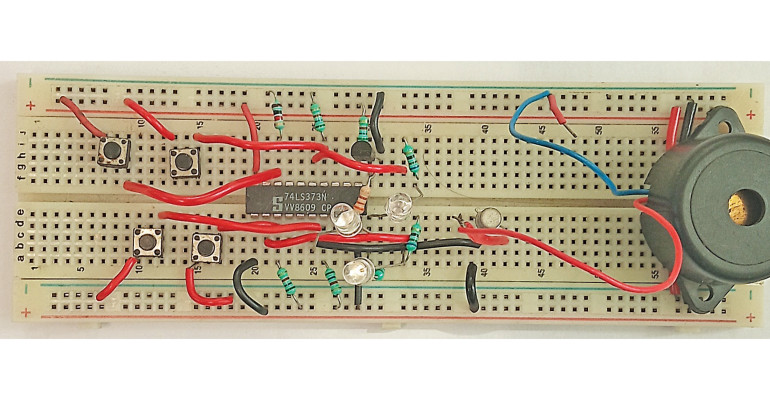

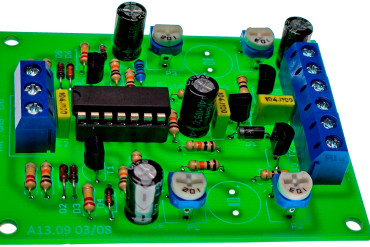

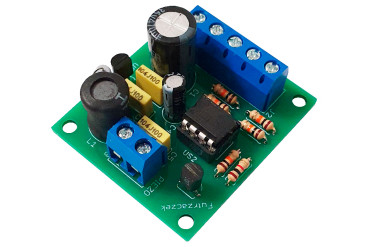

GŇā√≥wnymi podzespoŇāami sńÖ tu: transformator obniŇľajńÖcy napińôcie sieciowe (X1), mostek prostowniczy (BR1), stabilizator 5 V typu LM7805 (IC1), osiem przycisk√≥w niestabilnych (zwierajńÖcych styki po naciŇõnińôciu; S1 do S8), zatrzask typu 74LS373 (IC2), dwa tranzystory NPN 2N2219 (T1, T2), buzzer piezoelektryczny z generatorem (PZ1), dziewińôńá diod LED (LED1 do LED9) i ponadto kilka dyskretnych element√≥w pasywnych.¬†

UkŇāad zasilany jest napińôciem pozyskiwanym z sieci energetycznej 230 V AC za pomocńÖ typowego ukŇāadu zasilacza napińôcia staŇāego 5 V. Jest to zasilacz liniowy o niewielkiej sprawnoŇõci. Transformator obniŇľa napińôcie przemienne do poziomu 9 V, kt√≥re jest nastńôpnie prostowane dwupoŇā√≥wkowo mostkiem BR1, filtrowane pojemnoŇõcińÖ kondensatora C1 i nastńôpnie stabilizowane regulatorem liniowym LM7805. Kluczowym elementem jest zatrzask 74LS373.¬†

Przypis redakcji: 74LS373 skŇāada sińô z oŇõmiu niezaleŇľnych zatrzask√≥w typu D; praca ukŇāadu rozr√≥Ňľnia dwa stany. Albo jest ‚Äěprzezroczysty‚ÄĚ powielajńÖc wejŇõcie na wyjŇõcie, albo zapamińôtuje stan wejŇõńá w okreŇõlonej chwili czasowej; to zaleŇľy od stanu linii LE (Latch Enable). Linia OE (Output Enable) jest caŇāy czas aktywna (w stanie niskim); i w konstrukcji elementu jest przewidziana do wprowadzenia wyjŇõńá w stan wysokiej impedancji, co jest zwykle bardzo poŇľńÖdane w aplikacjach magistralowych.

Zatrzask IC2 74LS373 przenosi stan wejŇõńá D0 do D7 na wyjŇõcia Q0 do Q7. Wszystkie wejŇõcia (D0 do D7) wyposaŇľono w rezystory ŇõcińÖgajńÖce do stanu niskiego (R2 do R9). Do wejŇõńá podŇāńÖczone sńÖ takŇľe przyciski S1 do S8, kt√≥rych drugi koniec podŇāńÖczony jest do linii zasilania +5 V. Zatem naciŇõnińôcie dowolnego z nich wymusza stan wysoki (kt√≥ry nazwiemy jedynkńÖ logicznńÖ). Idea dziaŇāania ukŇāadu polega na tym, Ňľe naciŇõnińôcie dowolnego z przycisk√≥w S1 do S8 zaŇõwieca odpowiednińÖ diodńô na wyjŇõciu i uruchamia dŇļwińôk buzzera. R√≥wnoczeŇõnie w tym samym momencie ulega zmianie stan wejŇõcia LE z wysokiego na niski, co zatrzaskuje dane wejŇõciowe w przerzutnikach (stanowińÖcych elementarnńÖ pamińôńá cyfrowńÖ). Od tego momentu wyjŇõcia nie mogńÖ zmienińá swego stanu logicznego i stan ten utrzymuje sińô do momentu wyzerowania ukŇāadu. W obwodzie sprzńôŇľenia zwrotnego mińôdzy wyjŇõciami a wejŇõciem ‚ÄězatrzaskujńÖcym‚ÄĚ pracuje tranzystor T1 wraz z rezystorem R10. Tolerancja zasilania elementu 74LS373 to wńÖski przedziaŇā od 4,75 V do 5,25 V. Jest to jednak napińôcie typowe, a napińôcia stan√≥w logicznych zera i jedynki pozwalajńÖ na bezpoŇõrednie ŇāńÖczenie z ukŇāadami cyfrowymi wykonanymi w technologii CMOS, NMOS i TTL.