Ponieważ na pokładzie układu producent nie umieścił żadnego bloku nadającego się wprost do komunikacji bezprzewodowej (blok taki pojawia się dopiero w serii PSoC6 w postaci transceivera Bluetooth Low Energy), jedyny sposób wymiany informacji z otoczeniem zapewniają piny. Za ich pomocą układowi trzeba też dostarczyć z zewnątrz energię do pracy.

Stwierdzenia to mogą wydawać się trywialne, bo dokładnie tak samo jest w przypadku innych procesorów, ale jeśli przypomnimy sobie, do jakiego stopnia autonomicznymi i elastycznymi bytami są piny w układach PSoC, sprawa staje się daleka od prostej, do czego postaram się przekonać Czytelnika w dalszej części niniejszego odcinka.

Układy PLD - Jak działają piny zasilające?

Zacznijmy od pinów zasilających. Układy serii 5LP są dostępne wyłącznie w obudowach SMD w kształcie prostokąta (TQFP i QFN), co zostało wykorzystane w architekturze układu. Konkretnie, układ został podzielony na ćwiartki, z których każda zasilana jest z osobnej linii zasilającej VDDIOx. Piny wejścia-wyjścia należące do tej samej ćwiartki tworzą bank (na rysunku 1 wyróżnione kolorami).

Dzięki możliwości zasilania każdego banku innym napięciem układ może bez pomocy zewnętrznych translatorów poziomu pracować w środowiskach wielonapięciowych, np. 5V i 3,3V. Trzeba tylko zapewnić, by napięcie zasilania każdego z banków znajdowało się w zakresie 1,71–5,5V.

Użycie funkcji specjalnych (np. interfejsu USB) umieszczonych na pinach danego banku może jednak narzucić dodatkowe, wynikające ze specyfiki tej funkcji, ograniczenia na wartość napięcia VDDIO banku. Wspomniany interfejs USB działa poprawnie tylko przy zasilaniu 5V albo 3,3V. Należy to mieć na uwadze przy planowaniu sposobu wykorzystania pinów z danego banku.

Ponadto w każdym banku znajdują się dwa piny wejścia-wyjścia o licznych specjalnych własnościach. Noszą one nazwę SIO (Strong IO) i – gdy pracują jako wejścia – mogą być bezpośrednio podłączone do sygnałów logicznych o napięciach aż do 5,5V, niezależnie od napięcia zasilania banku. Dzięki wbudowanemu komparatorowi mogą też zostać połączone w parę różnicową o konfigurowalnym poziomie progowej różnicy sygnału. Na obu tych własnościach opiera się m.in. interfejs USB, ale możliwych zastosowań jest znacznie więcej.

Tyle dobrych wiadomości. Złe są takie, że ze względu na cenę i prostotę zestawu ewaluacyjnego CY8KIT-059 producent podłączył wszystkie linie zasilania do tego samego napięcia 5V, dostępnego na porcie USB, więc w trakcie niniejszego cyklu z wielonapięciowości nie skorzystamy.

Oprócz linii zasilania sekcji wejścia-wyjścia, na obudowie znajdują się jeszcze osobne linie zasilania bloków cyfrowych (VDDD) oraz analogowych (VDDA). Obie muszą znajdować się na potencjale z przedziału 1,8V–5,5V. Dowolność, jak widać, jest spora, trzeba tylko bezwzględnie pamiętać o tym, że napięcie „analogowe” VDDA z powodów technologiczno-konstrukcyjnych PSoC5LP musi być najwyższym napięciem w układzie!

Nie oznacza to jednak, że układy 5LP wymagają zasilania napięciami z podanego powyżej zakresu. Pozorna sprzeczność wynika z faktu, że wymienione linie zasilania nie są jedynymi dostępnymi na obudowie. Otóż do zastosowań niskonapięciowych seria 5LP ma przetwornicę podwyższającą (boost), która może pracować już od napięcia 0,5V! Jej wydajność jest jednak ograniczona do około 50mA. To niemało, ale trzeba mieć to na uwadze przy projektowaniu układu do nieco bardziej ekstremalnych zastosowań. Wykorzystanie przetwornicy jest oczywiście opcjonalne i w układach dysponujących dostatecznie wysokim napięciem zasilania związane z nią piny pozostawiamy niepodłączone.

Do przepływu prądu konieczne jest zamknięcie obwodu, więc na obudowie znajduje się odpowiednio dużo pinów masy, VSSx. Powinny one być połączone ścieżką o niskiej impedancji, co ma krytyczne znaczenie dla poprawnego działania układu, a zwłaszcza dla jego części analogowej. Ścieżki należy zaprojektować tak, by zmieniający się prąd obciążenia bloków cyfrowych nie wpływał na potencjał masy analogowej. Zazwyczaj osiąga się to poprzez połączenie mas cyfrowej i analogowej w tylko jednym punkcie, blisko wejścia (źródła) zasilania.

Dla kompletności obrazu trzeba przypomnieć, że czas propagacji sygnałów logicznych w każdym układzie półprzewodnikowym zależy od jego napięć zasilania i temperatury pracy. Dla zapewnienia poprawnego działania projektu PSoC Creator sprawdza więc czasy propagacji w najgorszych warunkach i odrzuca projekty wychodzące poza możliwości układu.

Z tego powodu do przeprowadzenia analizy trzeba mu dostarczyć informacji o napięciach zasilania i pożądanym zakresie temperatur pracy układu. Robi się to w zakładce Design Wide Resources (odtąd oznaczanej DWR) → System → Operating Conditions. Podczas tworzenia projektu trzeba zwrócić uwagę, by nie przesadzić zbytnio z wymaganiami i tym samym nie doprowadzić do odrzucenia przez syntezator zupełnie poprawnego układu. Problemom z czasem propagacji i sposobom ich rozwiązywania przyjrzymy się dokładniej w jednym z odcinków zaawansowanych, teraz wystarczy nam świadomość możliwości ich zaistnienia.

Układy PLD - Jak działają piny wejścia-wyjścia?

Pora na piny wejścia-wyjścia. Po pierwsze, musimy wyraźnie rozróżnić piny fizyczne i logiczne. Te pierwsze znajdują się na obudowie układu i możemy do nich podłączać inne elementy elektroniczne oraz urządzenia pomiarowe. Te drugie są z kolei abstrakcją, przedstawianą nam przez PSoC Creatora podczas pracy z projektem i na poziomie schematu nie mają żadnego powiązania z pinami fizycznymi.

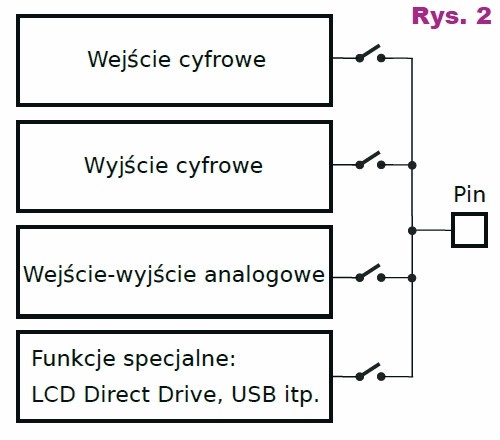

Ogólną strukturę pinu fizycznego przedstawia rysunek 2. Poprzez odpowiednie ustawienie przełączników pin może zostać podłączony do dowolnego z wymienionych bloków. Uwaga: nie jest to multiplekser; przełączniki pracują niezależnie, więc... ten sam pin może zostać podłączony do kilku bloków jednocześnie. Czasami będziemy korzystać z tej ciekawej własności. Ponadto, oprócz konfiguracji statycznie określonej w projekcie (przypadek typowy) stanem przełączników można sterować sprzętowo. W ten sposób można zrealizować m.in. analogowy multiplekser.

Interesującą i ważną funkcją układów 5LP jest możliwość indywidualnego określenia stanu każdego pinu podczas resetu. Oprócz stanu wysokiej impedancji można wymusić stan niski albo wysoki. Pozwala to pozbyć się z płytki rezystorów podciągających, ustalających układom współpracującym bezpieczną domyślną wartość logiczną. Ten stan początkowy jest pamiętany w dedykowanym bloku pamięci FLASH. Niestety, w odróżnieniu od głównej pamięci nieulotnej, blok ten ma deklarowaną wytrzymałość zaledwie 100 operacji zapisu, więc należy posługiwać się nim oszczędnie i w fazie prototypowania korzystać jednak z zewnętrznych rezystorów.

Jeżeli wydajność prądowa jednego pinu nie jest wystarczająca, można równolegle połączyć kilka pinów w grupę (pin ganging) i sterować stanem całego „gangu” pojedynczym sygnałem. Trzeba tylko pamiętać, by piny należały albo do tego samego banku, albo do różnych banków zasilanych tym samym napięciem.

Teraz słowo o funkcjach specjalnych: poza USB będą one przez nas rzadko wykorzystywane. W tym przypadku chodzi głównie o to, że układy PSoC5LP potrafią bezpośrednio sterować segmentowymi wyświetlaczami LCD. Pozwala to znacznie zmniejszyć liczbę elementów zewnętrznych i obniżyć koszty w konstrukcjach przemysłowych, ale dla hobbystów ma to marginalne znaczenie – my zazwyczaj korzystamy z wyświetlaczy LCD z wbudowanym kontrolerem.

Powiązanie pinów logicznych projektu z fizycznymi procesora

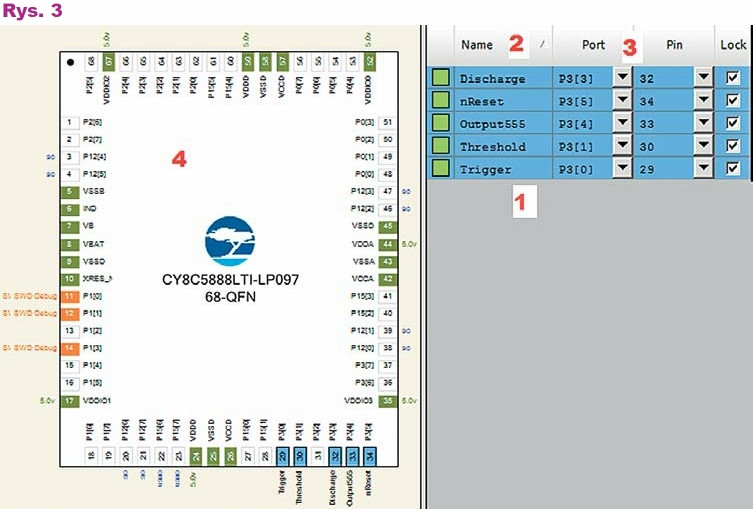

Finalnie trzeba jednak powiązać piny logiczne projektu z fizycznymi procesora. Służy do tego zakładka o intuicyjnej nazwie DWR → Pins (rysunek 3), z którą mieliśmy już do czynienia. W tabelce (1) po prawej stronie znajduje się lista występujących w projekcie pinów logicznych (Name – 2) oraz odpowiadających im odwzorowań fizycznych (Port, Pin – 3).

PSoC Creator samodzielnie proponuje mniej lub bardziej szczęśliwe odwzorowania, które jednak w każdej chwili możemy ręcznie zmienić za pomocą rozwijanych list w kolumnach Port i Pin. Przy okazji z list tych możemy się dowiedzieć, jakie inne funkcje (głównie analogowe) są preferowane na danym pinie fizycznym, co ułatwia świadome zaprojektowanie odwzorowań.

Piny przypisane przez użytkownika są oznaczane jako Locked, pozostałe zostaną wybrane przez automat z dostępnej puli. Jeżeli dany pin fizyczny został już przypisany jakiemuś pinowi logicznemu, a my wybierzemy go ponownie podczas konfiguracji innego pinu logicznego, poprzednie odwzorowanie zostanie usunięte i obowiązywać będzie nowe.

W praktyce jest to zachowanie wygodne i intuicyjne, ale łatwo może doprowadzić do pomyłki. Oczywiście pomyłka będzie łatwa do zauważenia, bo w tabelce zmieni się kolor wiersza „wywłaszczonego” pinu, niemniej należy klikać ostrożnie. Na szczęście opcja Cofnij pod skrótem Ctrl-Z działa poprawnie, więc ewentualną katastrofę można szybko opanować.

Stan przypisań w kontekście obudowy konkretnego układu można śledzić na bieżąco na obrazku po lewej stronie tabelki (4). Będzie to oczywiście obudowa przypisana do takiego modelu układu PSoC, jaki wskazaliśmy w początkowej fazie tworzenia projektu. Inne parametry, takie jak np. maksymalna częstotliwość taktowania układu do potrzeb analizy czasu propagacji, również są stamtąd automatycznie brane, co oszczędza nam wertowania dokumentacji i wpisywania ich ręcznie.

Możliwość wymodelowania układu na takim poziomie elastyczności byłaby jednak bezwartościowa, gdyby piny fizyczne nie pozwalały jej zrealizować układowo. A ponieważ pozwalają, natychmiast prowadzi nas to do wniosku o istnieniu w układzie sieci programowalnych połączeń. I to nie jednej: w rzeczywistości są dwie takie sieci. Ta przeznaczona do transportu sygnałów cyfrowych nazywa się DSI (Digital Signal Interconnect), analogowa w dokumentacji występuje pod prostą i oczywistą nazwą Analog Bus lub ABus.

Sieć DSI jest wszechobecna, ale nie mamy łatwego sposobu wniknięcia w jej wnętrzności, zazwyczaj pozostawiając to syntezatorowi. Nad siecią analogową mamy znacznie większą kontrolę (jeśli oczywiście chcemy, bowiem typowo i nią zajmuje się automat), co kiedyś omówimy dokładniej, bo jej zaawansowane wykorzystanie daje możliwości wręcz fantastyczne.

Układ 5LP - przykładowe ćwiczenie (kostka timera 555)

Teraz jednak wróćmy do podstaw, a te najlepiej będzie przećwiczyć na przykładzie. Na przykładzie niebanalnym!

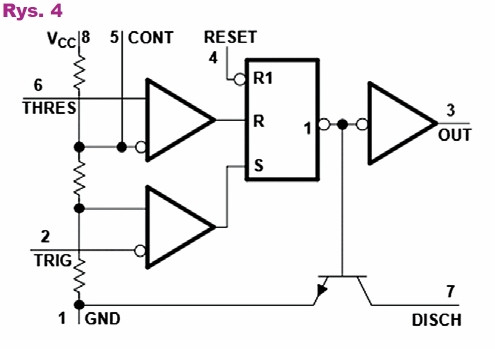

Otóż korzystając z zasobów układu 5LP, nie tylko odtworzymy sobie legendarną kostkę timera 555, ale natkniemy się po drodze na pouczające problemy. Nasz cel pokazuje schemat ideowy na rysunku 4. Widzimy na nim kilka pinów, dwa analogowe komparatory, sieć rezystorów, przerzutnik RS i tranzystor. No to do dzieła!

Tworzymy nowy pusty projekt (procesor CY8C5888LTI-LP097!), w zakładce System upewniamy się, że konfiguracja napięć zasilania jest poprawna i przechodzimy do edytora schematów, klikając na TopDesign.cysch na samym szczycie panelu sterowania, po lewej stronie. Z komparatorem pójdzie łatwo, bo mamy taki komponent w bibliotece.

W zakładce Component Catalog wpisujemy comparator i spośród wielu dostępnych opcji wybieramy bloczek Analog → Comparators → Comparator[v2.0]. PSoC Creator automatycznie nadał temu egzemplarzowi nazwę Comp_1, co nam nie przeszkadza. Klikamy na nim dwukrotnie i w okienku konfiguracyjnym doprecyzowujemy zachowanie komparatora.

Zazwyczaj histereza jest pożądana, więc włączamy (Hysteresis → Enable), wybieramy komparator szybki (kosztem większego zużycia energii, Speed → Fast), synchronizacji zboczy wyjściowych z zegarem nie chcemy, bo jeszcze nic nie wiemy o zegarach (Sync → Bypass), pozostałych ustawień nie zmieniamy. Czytelnicy pilni mogą w tym momencie od razu kliknąć przycisk OK albo Apply, a dociekliwi najpierw Datasheet. :)

Żarty na bok! Właśnie odkryliśmy kolejną potężną własność naszego zintegrowanego środowiska: dokumentację podręczną komponentów, z której będziemy intensywnie korzystać.

Drugi komparator możemy dodać albo powtarzając powyższą procedurę, albo klikając na pierwszy egzemplarz i wykonując kopiuj-wklej (z menu albo zwyczajowe Ctrl-C Ctrl-V z klawiatury). Druga możliwość bezbłędnie skopiuje nam również konfigurację, więc ją preferujemy.

Sprawa rezystorów wygląda na bardziej skomplikowaną, bo niczego podobnego na pokładzie układu 5LP niestety nie znajdziemy. Mówiąc słowami poety: jest dobrze, ale nie beznadziejnie. Możliwości wybrnięcia z problemu mamy co najmniej dwie. Pierwsza polega na przyjęciu do wiadomości odkrytego ograniczenia i wyprowadzeniu problematycznych węzłów dzielnika napięcia na pomocnicze piny analogowe. Rezystory dołączymy wówczas z zewnątrz wg oryginalnego schematu i jest oczywiste, że to będzie działać.

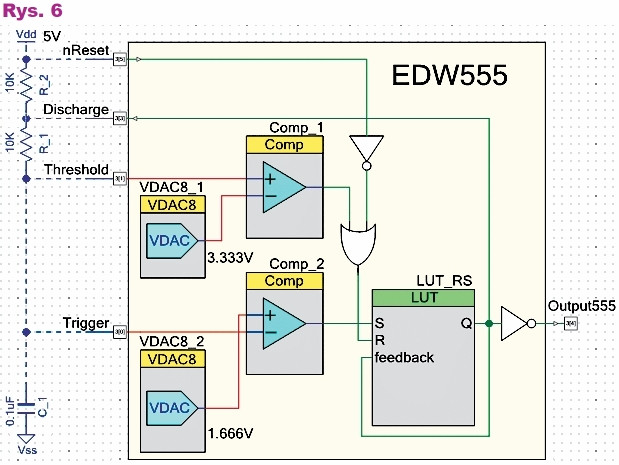

Drugie rozwiązanie polega na zrozumieniu, do czego te rezystory służą. Jest to prosty dzielnik napięcia, którego zadaniem jest wytworzyć 2/3 i 1/3 napięcia zasilania. Tak naprawdę potrzebujemy więc odpowiednich napięć, a nie rezystorów. A napięcia o potrzebnej wartości wytwarzać potrafimy, bo PSoC5LP ma na pokładzie aż cztery przetworniki DAC.

W Component Catalog wpisujemy „dac” i spośród wielu możliwości przeciągamy do schematu Analog →DAC → Voltage DAC (8-bit) [v1.90]. Klikamy na nim dwukrotnie i zmieniamy następujące ustawienia: Range → 0–4.080V i Voltage → 3333 [mV], bo tyle wynosi 2/3 z 5V napięcia zasilania. Wizard zmieni nam tę wartość na 3328mV, bo rozdzielczość DAC nie pozwala na wygenerowanie wartości dokładnie równej obliczonej przez nas. Nie szkodzi! Rezystory też mają swoje tolerancje, i to znacznie większe.

Klonujemy DAC i w drugim egzemplarzu ustawiamy Voltage na 1666, z czego robi się 1664mV. Możemy teraz podłączyć DAC-e do komparatorów. Tryb edycji połączeń aktywuje się albo ikonką „wężyka” z menu edytora schematów, albo klawiszem „w”. PSoC Creator z kontekstu domyśli się, czy tworzymy połączenie analogowe, czy cyfrowe, więc nie ma potrzeby wymuszania tego. Te połączenia niosą sygnały analogowe, więc będą pomarańczowe.

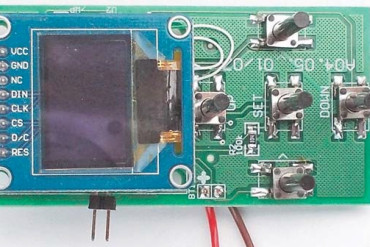

Do zakończenia sekcji wejściowej brakuje nam tylko pinów, więc w katalogu wpisujemy „pin” i przeciągamy na schemat komponent Ports and Pins → Analog Pin [v2.20]. Od razu tworzymy jego dwie kopie. Wywołujemy ich okna konfiguracyjne poprzez dwukrotne kliknięcie na egzemplarzu i jednemu zmieniamy nazwę na Trigger, a drugiemu na Threshold, zgodnie z oryginalnym schematem.

Piny podłączamy do komparatorów i możemy przystąpić do modelowania sekcji cyfrowej. Na schemacie umieszczamy egzemplarz przerzutnika RS (Digital → Logic → SR Flip Flop [v1.0]) oraz pin cyfrowego wejścia (Ports and Pins → Digital Input Pin [v2.20]). Pin nazywamy sobie nReset i... tu pojawiają się dwa problemy (a nawet cztery, o czym dalej). Po pierwsze, nasz przerzutnik ma tylko jedno wejście R, a ten w 555 ma dwa. Nie jest to jednak żaden kłopot, bo przecież w katalogu mamy bramkę OR (Digital → Logic → Or [v1.0]), za pomocą której możemy sobie zwielokrotnić dowolne wejście.

Drugi problem uwidacznia się w dokumentacji przerzutnika. On pracuje w logice dodatniej, a wejście Reset układu 555 w ujemnej. Wartość wejścia trzeba więc będzie zanegować (Digital → Logic → Not [v1.0]). Mając to wszystko, przystępujemy do wymodelowania kolejnego fragmentu sieci połączeń. Zauważamy, że tym razem przewody są koloru zielonego, bo sygnały są cyfrowe.

Możemy teraz przystąpić do odtworzenia sekcji wyjściowej układu 555. Jak się okazuje, wyjścia są dwa. Pierwsze nazywa się „Output” i jego stan odzwierciedla stan wyjścia przerzutnika. Sprawa jest więc prosta: wyszukujemy słowa „pin”, przeciągamy komponent na schemat (Port and Pins → Digital Output Pin [v2.20]). Podłączamy go do wyjścia przerzutnika i nazywamy np. „Output555”, bo niestety krótkie „Output” jest słowem zarezerwowanym i nie przechodzi przez walidator.

Drugie wyjście układu 555 nazywa się „Discharge” i służy do rozładowywania kondensatora. Tu znów jest kłopot, bo pojedynczych tranzystorów też nie ma w układach 5LP. Jest to jednak tylko problem pozorny, bo dokładnie tak samo zachowuje się wyjście z otwartym drenem. Klonujemy więc nasz pin Output555 i wchodzimy w jego konfigurację. Zmieniamy nazwę, a następnie w zakładce General → Drive Mode wybieramy Open drain, drives low. Wyjście Discharge łączymy równolegle z wyjściem Output555 i... mamy nasz własny timer 555.

No, prawie...

Nie podłączyliśmy wejścia clk przerzutnika, a niestety komponent SR dostępny w katalogu gotowców jest przerzutnikiem synchronicznym. Możemy go podłączyć do dowolnego dostatecznie szybkiego zegara (z punktu widzenia stałej czasowej wyznaczonej przez elementy RC podłączone do układu 555) i to rozwiąże problem. Druga sprawa jest poważniejsza i o niej też możemy dowiedzieć się z dokumentacji przerzutnika: jest to przerzutnik z dominującym wejściem S! Oznacza to, że jeśli przerzutnik jednocześnie otrzyma polecenia R i S, to zastosuje się do ostatniego z nich. Niestety, przerzutnik w 555 działa dokładnie odwrotnie!

Rozwiązania są trzy, ale niestety żadne z nich nie jest idealne. Pierwsze polega na utworzeniu własnego komponentu i wymodelowaniu dokładnie takiego zachowania, jakiego potrzebujemy. Niestety, nie potrafimy jeszcze ani tworzyć własnych komponentów, ani programować w Verilogu.

Drugie rozwiązanie opiera się na spostrzeżeniu, że w przerzutniku RS stan R nie różni się niczym istotnym od stanu S i w gruncie rzeczy interpretacja stanu przerzutnika sprowadza się tylko do konwencji, które z wyjść Q i ~Q umówimy się traktować jako wyjście odniesienia. Mówiąc inaczej, na schemacie możemy zamienić połączenia wejść R i S miejscami i zanegować wyjście. Wynikowy przerzutnik będzie przerzutnikiem z dominującym stanem R. Od strony technicznej będzie to rozwiązanie poprawne, ale za cenę zaciemnienia schematu.

Trzecie rozwiązanie polega na próbie stworzenia brakującego komponentu metodą... chałupniczą. W katalogu znajdziemy komponent LUT (Digital → Logic → Lookup Table [v1.60]), który służy do modelowania funkcji za pomocą tabeli prawdy. Jeśli wyjście układu podamy również na jego wejście, otrzymamy możliwość modelowania układów sekwencyjnych. Skorzystamy też z faktu, że wejście zegarowe jest opcjonalne w LUT, co pozwoli wymodelować przerzutnik asynchroniczny i rozwiązać problem „niechcianego” zegara w komponencie SR z biblioteki. Ustalenie zawartości tabeli prawdy LUT Szanowny Czytelnik zechce potraktować jako zadanie domowe.

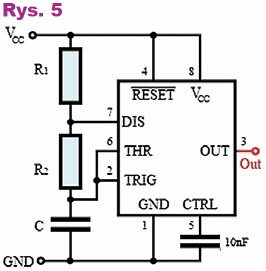

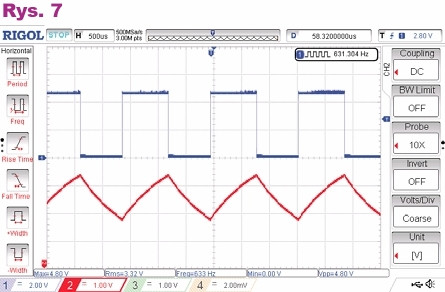

Ja zdecydowałem się na właśnie takie rozwiązanie. W celu przetestowania układu podłączyłem go w klasycznej konfiguracji multiwibratora astabilnego (rysunek 5), co prowadzi do finalnego schematu przedstawionego na rysunku 6. Po zbudowaniu projektu zaprogramowałem procesor. Oscylogram (rysunek 7) pokazuje poprawną pracę „mojego” 555: przebieg niebieski to stan wyjścia Output555, a czerwony to napięcie na kondensatorze C1. Czytelnicy niedysponujący oscyloskopem mogą działanie układu sprawdzić np. głośniczkiem podłączonym przez kondensator 100nF.

Z zakładki Resource Meter dowiemy się, że zużycie zasobów PLD jest niewielkie: zaledwie 2 makrocele ze 192 dostępnych, choć na schemacie mamy aż 3 bramki i dość skomplikowaną tablicę LUT.

W odróżnieniu od części PLD i pinów, komponenty analogowe niestety nie uruchamiają się same, więc krótki program w pliku main.c ma za zadanie tylko ich wystartowanie. Późniejsze działanie multiwibratora odbywa się bez ingerencji procesora. Projekt jest dostępny na Elportalu, a my w następnym odcinku zajmiemy się zegarami.