W praktyce każdego elektronika zajmującego się techniką cyfrową wcześniej czy później musi nadejść taki moment. Mowa o chwili, w której trudno mu się obejść bez choćby prostego analizatora stanów logicznych, który jak się wydaje, powinien być elementarnym wyposażeniem takiego warsztatu. Tak samo było i w moim przypadku. Prace rozpocząłem od poszukiwania ciekawych rozwiązań istniejących układów, lecz szybko okazało się, iż rozwiązania te nie satysfakcjonują mnie. Generalnie, urządzenia, których opisy znalazłem w Internecie, można podzielić na dwie grupy: średnioskomplikowane układy akwizycji danych współpracujące z komputerem klasy PC i dedykowaną im aplikacją lub układy autonomiczne, lecz o ograniczonej funkcjonalności.

Postanowiłem skonstruować urządzenie szyte na miarę moich potrzeb. Jako że jestem zdecydowanym zwolennikiem urządzeń funkcjonujących samodzielnie, zdecydowałem się zbudować samodzielnie funkcjonujący układ.

Opis konstrukcji

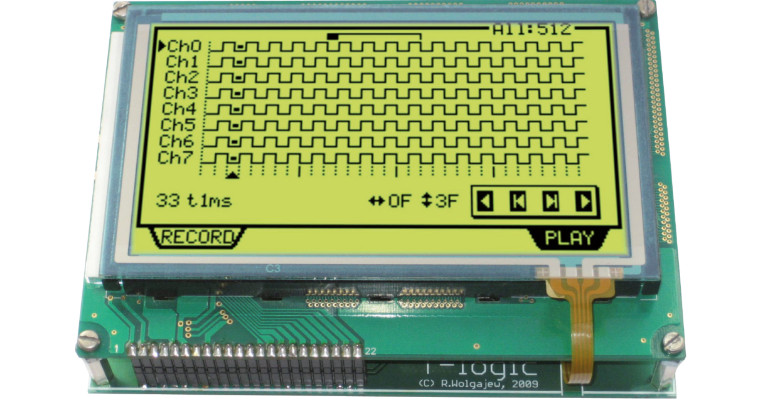

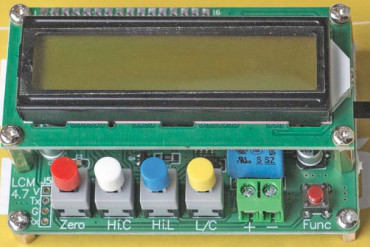

Jest to urządzenie z mikrokontrolerem o średniej skali komplikacji, wykorzystujące mikrokontroler ATmega325, kilka typowych układów scalonych z serii 74HC (lub HCT) oraz wyświetlacz graficzny LCD o rozdzielczości 240×128 punktów, zintegrowany z rezystancyjnym panelem dotykowym.

Nie bez powodu (jak i pewnych trudności) wybrano ten, a nie inny układ z rodziny AVR. Po pierwsze, zapewnia on odpowiednią liczbę portów I/O. Po drugie, wyposażono go w niezbędną z punktu widzenia założeń projektowych, liczbę źródeł przerwań sprzętowych. Po trzecie, układ ten dysponuje odpowiednią liczbą układów czasowo-licznikowych, jak i wbudowanym przetwornikiem ADC niezbędnym do obsługi panelu dotykowego.

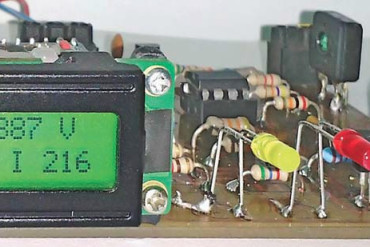

Głównym zadaniem mikrokontrolera jest sterowanie procesem akwizycji i analizy danych oraz obsługa wyświetlacza zintegrowanego panelem dotykowym i graficznego interfejsu użytkownika. W analizatorze wykorzystano wszystkie układy czasowo-licznikowe mikrokontrolera oraz 3 źródła przerwań sprzętowych. Do składowania zarejestrowanych danych zastosowano statyczną pamięć RAM o oznaczeniu HM62256B o pojemności 32 kB, zaś do jej adresowania dwa 12-bitowe liczniki binarne typu 74HC4040 (używane jest 15-bitowe słowo adresowe).

Pomimo iż podprogramy obsługi przerwań zostały napisane w asemblerze, a wykonanie każdego z nich zajmuje tylko kilka taktów zegara mikrokontrolera, to biorąc pod uwagę, że czas upływający od momentu wystąpienia zdarzenia generującego przerwanie do rozpoczęcia jego obsługi w mikrokontrolerach AVR zajmuje cztery cykle maszynowe, to przy częstotliwości taktującej wynoszącej 16 MHz nie da się uzyskać większej aniżeli 1 MHz realnej częstotliwości próbkowania sygnałów badanych.

Na rysunku przedstawiono w sposób schematyczny blok logiki sprzętowej analizatora wraz z rysunkiem przebiegów w charakterystycznych punktach układu dla trybu akwizycji danych „RECORD”. W analizatorze zastosowano dodatkowe, sprzętowe zabezpieczenie przed przekroczeniem górnego adresu pamięci RAM w trybie akwizycji danych (pomimo implementacji procedury OVF1) w przypadku, gdy wybrano maksymalną, dostępną liczbę próbek czyli 32768. Do tego celu służy wyjście Q4 licznika binarnego 74HC4040 (U5), bramka NAND U8D oraz jedno z wejść bramki NAND U8A. Zgodnie z tym co napisano wcześniej, układ Timer0 dostarcza sygnał taktujący procesem akwizycji danych. W tym celu, układ ten skonfigurowano do pracy w trybie CTC licznika (wyjście OC0A w tryb Toggle) z odpowiednimi ustawieniami rejestru OCR0A jak i preskalera (N) częstotliwości taktującej ten licznik.

Dodatkowo, kilka słów wyjaśnienia wymagają sygnały sterujące dostępne na wybranych portach mikrokontrolera, których znaczenie jest fundamentalne z punktu widzenia sposobu pracy urządzenia.

Pomimo tego, że pamięć RAM w trybie akwizycji danych adresowana jest całkowicie sprzętowo, to tenże sam proces w trybie analizy danych, kontrolowany jest wyłącznie programowo. To znaczy, że odpowiedni przebieg taktujący (na wyjściu OC0A) generowany jest programowo bez użycia układu Timer0. Wynika to przede wszystkim z wybranego sposobu adresowania pamięci RAM jak i zapewnienia możliwości dowolnego przewijania rekordu danych (zawartości pamięci RAM). Dla zminimalizowania niekorzystnych zjawisk, które mogą wystąpić na wejściach układu zatrzasku 74HC573, zdecydowano się na zbocznikowanie ich do masy za pomocą rezystorów 220 kΩ. Dużo lepszym rozwiązaniem jest zastosowanie specjalizowanych izolatorów cyfrowych np. układów ADuM1400 firmy Analog Devices.