Forum Micro-Cap 12

Jeśli chodzi o program Micro-Cap 12, to odkryliśmy, że niedawno zostało uruchomione forum online użytkowników: „Użytkownicy Micro-Cap EDA” pod adresem mc12.createaforum.com.

Czytelnicy zainteresowani korzystaniem z tego oprogramowania mogą uznać to forum za przydatne źródło informacji. To niegdyś drogie oprogramowanie zostało udostępnione bezpłatnie w lipcu 2019 r. po zatrzymaniu prac rozwojowych, w związku z czym nie ma już oficjalnego wsparcia.

Podsumowanie synchronicznego taktowania obwodu

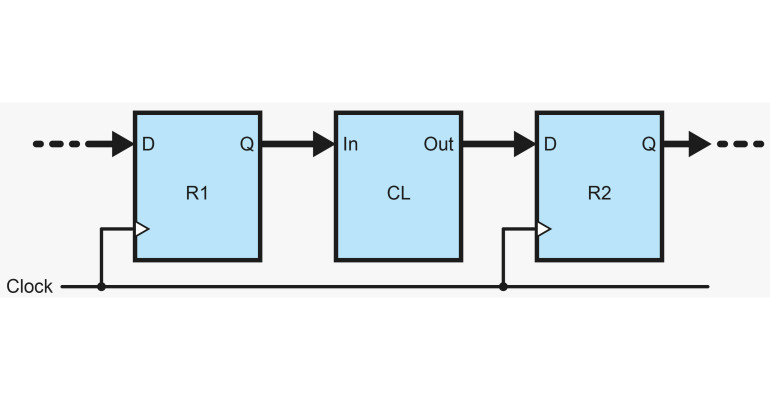

Obwód dzielnika był stosunkowo nietypowy, ponieważ został zaprojektowany przy użyciu minimalnej liczby bramek NAND i technik projektowania asynchronicznego, a nie tylko przy użyciu istniejącego gotowego przerzutnika. Dlatego w zeszłym miesiącu przyjrzeliśmy się problemom synchronizacji, w znacznie bardziej powszechnym kontekście synchronicznych obwodów cyfrowych. Obwody synchroniczne są sterowane sygnałem zegarowym – regularnym ciągiem impulsów, który kontroluje ogólne taktowanie obwodu. Nawet jeśli obwód synchroniczny ma złożoną ogólną strukturę, to zasadniczo obejmuje transfery między rejestrami, tak jak pokazano to na rysunku tytułowym – dane przechowywane w rejestrze (R1) są przetwarzane przez logikę kombinacyjną (CL), a wynik jest zapisywany w (R2). W każdym cyklu zegara, (R1) ładuje nowe dane do przetworzenia, a (R2) przechowuje wynik przetwarzania danych, które były przechowywane w R1 w poprzednim cyklu zegara.

Obwód na rysunku tytułowym nie jest nieskończenie szybki. Występuje w nim opóźnienie od chwili wystąpienia aktywnego zbocza zegara do zmiany wyjścia rejestru (TDR) oraz opóźnienia od zmiany wejść logiki kombinacyjnej do chwili, w której możemy zagwarantować, że jej wyjścia są prawidłowe. Musimy również wziąć pod uwagę, że gdy dane się zmieniają, to wewnętrzne obwody przerzutnika potrzebują czasu, aby dostosować się do tej zmiany. Jeśli zegar zostanie aktywowany zbyt blisko zmiany danych, przerzutnik może nie działać poprawnie (mówimy wtedy, że nastąpiło naruszenie taktowania). Może on załadować niewłaściwą wartość lub stać się metastabilny, co może skutkować znacznie dłuższym niż zwykle opóźnieniem przed zmianą sygnału wyjściowego. Aby zapobiec naruszeniom taktowania, przerzutniki mają określone czasy: ustalenia (TSetup) i czas podtrzymania (Thold) – tj. czas przed i po zboczu zegara, podczas którego dane nie mogą się zmieniać, aby zapewnić prawidłowe działanie.

Naruszenia taktowania

Jak to omówiono w zeszłym miesiącu, dla obwodu z rysunku 1 minimalny okres zegara musi być większy niż TDR + TDC + TSetup, aby mieć pewność, że dane załadowane do (R2) są prawidłowe. W obwodzie synchronicznym możemy to zapewnić konstrukcyjnie, co oznacza, że nie będą w nim występowały naruszenia taktowania. Niekoniecznie jest to łatwe, szczególnie w przypadku dużych projektów, gdzie wymagania dotyczące wydajności wymagają wysokich częstotliwości taktowania. Profesjonalne narzędzia do projektowania dużych obwodów cyfrowych (np. projektowania FPGA) zawierają analizatory taktowania, które pomagają zidentyfikować problemy z synchronizacją. Źródła problemów z synchronizacją są bardziej złożone niż tylko warunek odpowiedniego okresu zegara, o którym wspomnieliśmy powyżej. Na przykład w dużym projekcie zegar nie dotrze do każdego przerzutnika dokładnie w tym samym czasie (nazywa się to przesunięciem zegara), co również może powodować naruszenia synchronizacji. Niemniej jednak, przy pewnym wysiłku, można zapewnić, że w obwodzie synchronicznym z pojedynczym zegarem nie wystąpią naruszenia taktowania.

„Gwarancja konstrukcyjna” nie ma zastosowania, gdy mamy zewnętrzne sygnały asynchroniczne – mogą one zmieniać się w dowolnym momencie cyklu zegara, co oznacza, że mogą zmieniać się także wystarczająco blisko aktywnego zbocza zegara, aby spowodować naruszenie taktowania. Podobnie w obwodach z wieloma zegarami (domenami zegara) istnieje możliwość naruszenia synchronizacji, gdy sygnały przekraczają domeny zegara. Istnieje pewien czas (okno metastabilności, T0), w którym zmiany danych, podczas taktowania zatrzasku spowodują metastabilność. Jeśli taka wystąpi to zatrzaskowi zajmie trochę czasu, zwanego „czasem rozdzielczości” (TR), zanim powróci on do jednego ze stanów stabilnych. Teoretycznie wartość ta może być nieskończona, ale w praktyce jest bardziej prawdopodobne, że będzie się mieścić w zakresie do około dziesięciokrotności czasu opóźnienia propagacji (TDR). W przypadku sygnałów asynchronicznych nie mamy kontroli nad względnym taktowaniem sygnału, dlatego nie możemy zagwarantować, że zapobiegniemy metastabilności. Musimy sobie z tym poradzić w kategoriach prawdopodobieństwa, które omówimy szerzej za chwilę.