Rozdzielczość, dokładność oraz szumy kwantyzacji - przetworniki sigma-delta

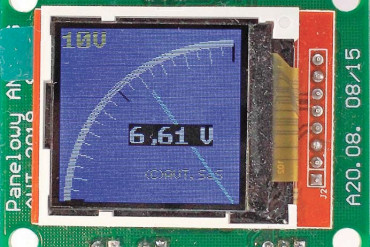

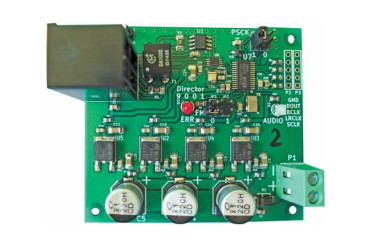

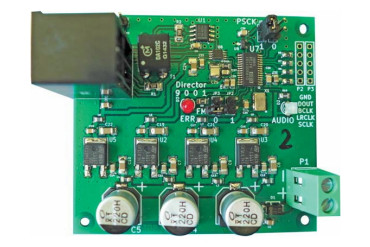

Aktualnie większość precyzyjnych przetworników ADC to przetworniki sigma-delta. Trzeba jednak pamiętać, że ich realna dokładność – precyzja, jest mniejsza od deklarowanej rozdzielczości bitowej. Przykładowo przetwornik ΣΔ oznaczony AD7177-2 reklamowany jest jako 32-bitowy o prędkości przetwarzania 10kSPS – rysunek 1. Czyli na wyjściu daje wynik pomiaru o ogromnej rozdzielczości, mianowicie w postaci liczby 32-bitowej.

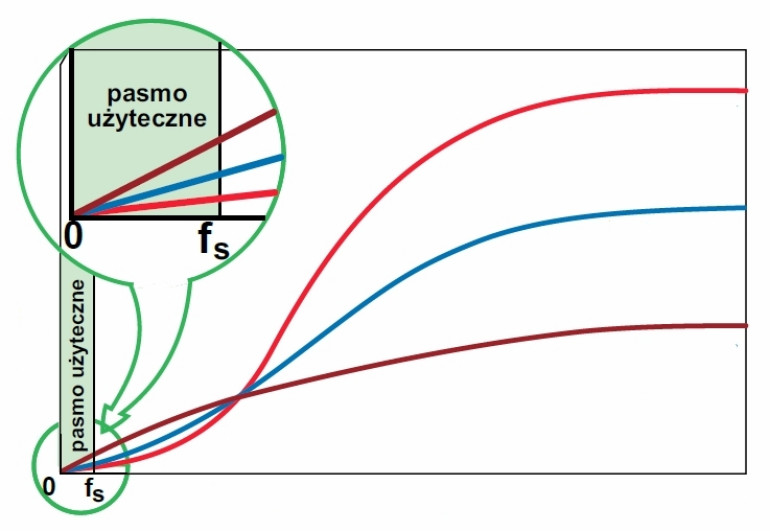

Owszem daje, ale zgodnie z rysunkiem 2 przy częstotliwości 10kSPS (10 000 pomiarów na sekundę), zależnie od konfiguracji, spośród tych 32 bitów tylko 18,7...21,9 najstarszych bitów zawiera czystą, wierną informację. Pozostałe zawierają szum – przypadkowe dane. Maksymalną precyzję przetwornik ten osiąga przy przetwarzaniu 5 próbek na sekundę (5SPS), ale też nie są to 32 bity, tylko 24,6...27,3 bita wiernej, czystej, bezszumnej informacji, natomiast najmłodsze bity też zawierają szumy – przypad...