Termin â€poziom logiczny†odnosi siؤ™ do napiؤ™ؤ‡ uإ¼ywanych do reprezentowania logicznych jedynek i zer w obwodach cyfrowych. Zazwyczaj projektujemy ukإ‚ady logiczne, rozwaإ¼ajؤ…c tylko jedynki i zera danych oraz sygnaإ‚أ³w sterujؤ…cych w kombinacjach lub sekwencjach. Jednakإ¼e bramki logiczne i przerzutniki, z ktأ³rych zbudowane sؤ… takie obwody, sؤ… z kolei realizowane za pomocؤ… tranzystorأ³w – i obwody te majؤ… wإ‚aإ›ciwoإ›ci analogowe, jeإ›li przyjrzymy siؤ™ relacjom miؤ™dzy ich wejإ›ciami, wyjإ›ciem i napiؤ™ciami zasilajؤ…cymi na wystarczajؤ…cym poziomie szczegأ³إ‚owoإ›ci. W wiؤ™kszoإ›ci przypadkأ³w nie trzeba siؤ™ tym przejmowaؤ‡ – moإ¼liwe jest projektowanie procesorأ³w z dziesiؤ™cioma miliardami tranzystorأ³w, poniewaإ¼ moإ¼emy pominؤ…ؤ‡ analogowe aspekty obwodأ³w i zajmowaؤ‡ siؤ™ jedynie cyfrowؤ… reprezentacjؤ… sygnaإ‚أ³w.

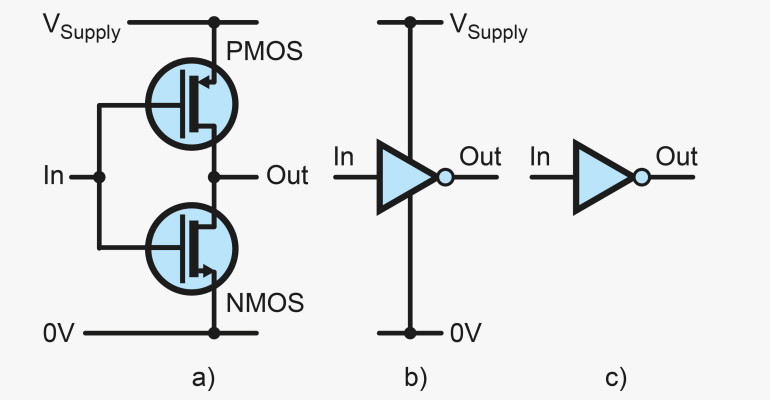

Czasami jednak musimy braؤ‡ pod uwagؤ™ rzeczywiste napiؤ™cia i inne â€analogowe†wإ‚aإ›ciwoإ›ci obwodأ³w logicznych, na przykإ‚ad gdy إ‚ؤ…czymy urzؤ…dzenia z rأ³إ¼nych rodzin technologicznych, pracujؤ…ce przy rأ³إ¼nych napiؤ™ciach zasilania lub gdy rozwaإ¼amy wpإ‚yw zakإ‚أ³ceإ„ elektrycznych na dziaإ‚anie obwodu. Aby podkreإ›liؤ‡ potencjalne rأ³إ¼nice pomiؤ™dzy obwodami, przyjrzymy siؤ™ pokrأ³tce dwأ³m kluczowym typom ukإ‚adأ³w logicznych – CMOS i TTL – a nastؤ™pnie przyjrzymy siؤ™ szczegأ³إ‚owo napiؤ™ciom logicznym i praktycznemu przykإ‚adowi ich إ‚ؤ…czenia.

W tym artykule uإ¼ywamy terminأ³w â€technologie logiczne†i â€rodziny ukإ‚adأ³w logicznychâ€. â€Technologie†odnoszؤ… siؤ™ do procesأ³w wytwarzania stosowanych do produkcji wszystkich typأ³w ukإ‚adأ³w scalonych, w tym na przykإ‚ad mikroprocesorأ³w wysokiej klasy. Technologia okreإ›la rodzaj i wielkoإ›ؤ‡ stosowanych tranzystorأ³w oraz wiele charakterystyk, takich jak szybkoإ›ؤ‡ i zuإ¼ycie energii.

â€Rodzina ukإ‚adأ³w logicznych†odnosi siؤ™ bardziej szczegأ³إ‚owo do rأ³إ¼nych zakresأ³w podstawowych elementأ³w logicznych (takich jak bramki, przerzutniki, rejestry i liczniki) produkowanych przez producentأ³w takich jak Texas Instruments.

Kaإ¼da rodzina ukإ‚adأ³w logicznych jest realizowana w okreإ›lonej technologii i wykorzystuje okreإ›lone podejإ›cie do projektowania bramek logicznych na poziomie pojedynczego tranzystora.