Do czego to służy? - uniwersalny dzielnik częstotliwości

Zlicza on kolejne zbocza narastające wejściowego sygnału prostokątnego. Po odliczeniu zadanej przez użytkownika liczby impulsów generuje jeden impuls o z góry ustalonym czasie trwania. W ten sposób da się N-krotnie zmniejszyć częstotliwość sygnału, gdzie N można ustalić zworką z przedziału od 1 do 9.

Górna częstotliwość pracy układu jest określona nakładaniem się kolejnych impulsów wyjściowych i przy podanych wartościach elementów wynosi ok. 13,5kHz (na wyjściu układu). Dolna częstotliwość nie jest określona, może być dowolnie niska.

Jak działa uniwersalny dzielnik częstotliwości?

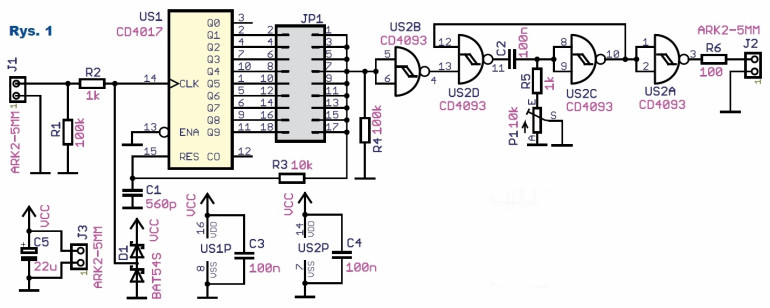

Schemat ideowy układu znajduje się na rysunku 1. Nie zawiera układów programowalnych, więc jego analiza nie będzie skomplikowana nawet dla początkujących elektroników.

Sygnał wejściowy jest podawany na złącze J1. Rezystor R1 ustala niski stan logiczny na wejściu przy braku podł ączonego źródła, aby układ nie reagował na przypadkowo pojawiające się zakłócenia.

Rezystor R2 i duodioda D1 tworzą ogranicznik amplitudy napięcia wejściowego. Kiedy wartość chwilowa napięcia będzie chciała spaść poniżej ok. –0,3V, otworzy się dolna dioda. Jeżeli zaś spróbuje wzrosnąć o 0,3V powyżej napięcia zasilającego, otworzy się górna dioda. Podwójna dioda typu BAT54S jest dedykowana do pracy w tego typu obwodach zabezpieczających. Rolą rezystora R2 jest ograniczenie prądu płynącego przez aktualnie otwartą diodę oraz zwiększenie czasu narastania napięcia, aby był czas na jej otwarcie.

Do zliczania impulsów został wykorzystany dziesiętny licznik Johnsona zawarty w układzie CD4017. Jego wielką zaletą jest dziesięć wyjść, z których każde może posłużyć do „skrócenia” licznika – wystarczy połączyć odpowiednie wyjście Q1…Q9 z wejściem zerującym RST (nóżka 15), w wyniku czego uzyska się podział przez 1…9. Wyjście Q0 jest w tej aplikacji nieużywane, ponieważ podział częstotliwości przez 0 jest bezcelowy – układ zawiesza się. Wyboru dokonuje użytkownik poprzez założenie zworki na odpowiednią parę szpilek.

Pojawienie się stanu wysokiego na wybranym wcześniej wyjściu powoduje wyzwolenie multiwibratora monostabilnego, który generuje jeden impuls. Jednak było konieczne wydłużenie czasu reakcji układu US1 na sygnał zerujący, czego dokonano przy użyciu prostego układu RC, składającego się z elementów R3 i C1. Ładowanie kondensatora przez rezystor wprowadza opóźnienie, co wydłuża czas trwania stanu wysokiego na wybranym wyjściu. Bez tego układu opóźniającego impuls zerujący trwał około 200ns i był zbyt krótki, aby wyzwolić generator monostabilny.

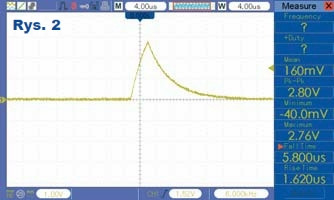

Przebieg na wejściu RST wygląda tak, jak na rysunku 2. Zbocze narastające jest znacznie krótsze od opadającego, ponieważ różne są asymptoty tych krzywych wykładniczych. Pierwsza (narastająca) dąży do napięcia zasilania (tutaj 5V), a druga (opadająca) do potencjału masy (0V). Wydłużenie czasu narastania i opadania sygnału zerującego jest na tyle małe, że prawidłowo wysteruje on nawet wejście nieopatrzone przerzutnikiem Schmitta.

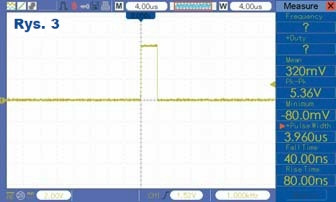

Efektem wydłużenia reakcji układu na sygnał zerujący jest dłuższy impuls wyzwalający przerzutnik monostabilny, którego przebieg widać na rysunku 3. Trwa on ok. 4μs, a jego zbocza są strome. Przebieg czasowy tego napięcia zarejestrowano na zaciskach rezystora R4, którego zadaniem jest utrzymywanie niskiego stanu logicznego na wejściach bramki US2B w sytuacji, gdyby użytkownik zapomniał nałożyć zworkę.

Na przerzutnik monostabilny składają się tylko dwie bramki NAND: US2D i US2C. W stanie spoczynku na obu wejściach bramki US2C panuje niski stan logiczny, wymuszony rezystorami, więc stan logiczny na jej wyjściu jest wysoki. Wyjście bramki US2B również jest w stanie wysokim, więc bramka US2D „widzi” dwa stany wysokie – zgodnie z zasadą działania bramki NAND stan jej wyjścia jest niski. Kondensator C2 jest rozładowany, ponieważ potencjały obu jego okładek są równe 0V.

Po nadejściu impulsu wyzwalającego, który bramka US2B neguje, jedno z wejść bramki US2D na chwilę przyjmuje stan niski, przez co stan jej wyjścia ulega zmianie na wysoki. Kondensator C2, na mocy prawa komutacji, nie przeładowuje się natychmiastowo, więc również stan logiczny na wejściach US2C staje się wysoki. Bramka US2C wprowadza negację, przez co bramka US2D nadal widzi na co najmniej jednym wejściu „0”, nawet po zaniku impulsu wyzwalającego.

W tym czasie kondensator C2 powoli się ładuje – ładunek dopływa poprzez połączone szeregowo R5 i P1. Jeżeli potencjał jego lewej okładki zmaleje na tyle, że przez bramkę US2C zostanie uznany za niski, stan logiczny wyjścia przerzutnika wraca do poziomu wysokiego i układ czeka na ponowne wyzwolenie.

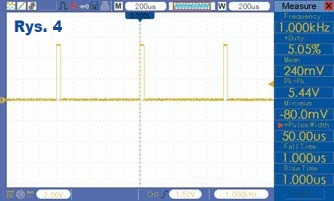

Czas trwania wygenerowanego impulsu reguluje się potencjometrem P1. W jednym skrajnym położeniu, gdy ma minimalną rezystancję, impuls wyjściowy trwa ok. 50μs (rysunek 4). W drugim skrajnym położeniu jego ślizgacza, czas ten wzrasta do ok. 1,3ms (rysunek 5).

Jednak pomiędzy kolejnymi impulsami muszą istnieć pewne przerwy, związane z przygotowaniem przerzutnika monostabilnego do kolejnego impulsu (tzw. czas martwy). Związane jest to z koniecznością rozładowania kondensatora C2, które tutaj odbywa się w większości przez diody zabezpieczające wejścia bramki US2C. Stąd wynika (wyznaczone doświadczalnie) ograniczenie maksymalnej częstotliwości wyjściowej do 13,5kHz – przy ustawieniu najkrótszego impulsu wyjściowego.

Zbudowany w ten sposób przerzutnik monostabilny jest wyzwalany impulsem mającym stan niski i taki sam impuls generuje – dlatego wyjście układu obsługuje bramka US2A, która zapewnia pojedynczy impuls o polaryzacji dodatniej.

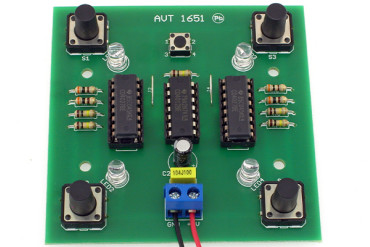

Montaż i uruchomienie uniwersalnego dzielnika częstotliwości

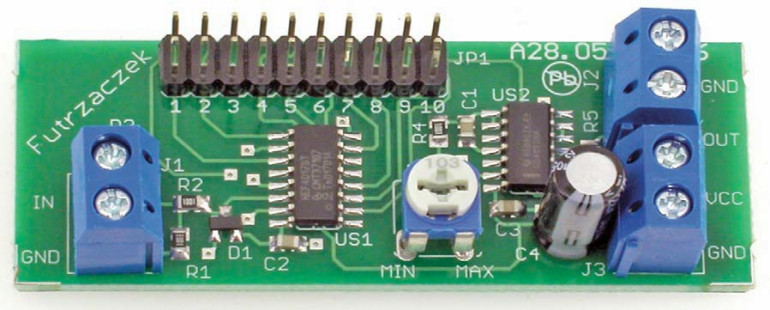

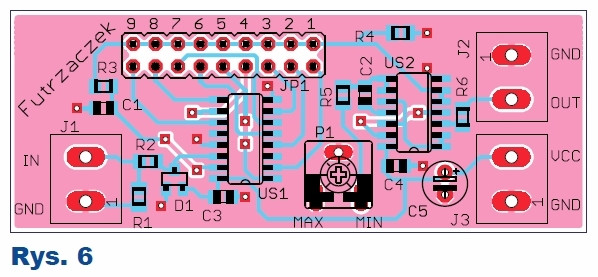

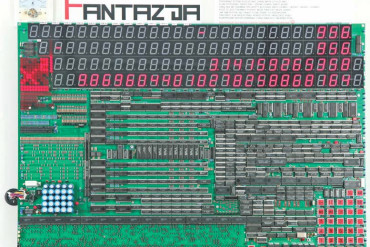

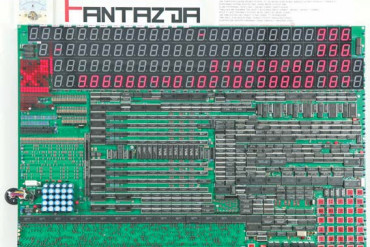

Układ prototypowy został zmontowany na dwustronnej płytce drukowanej o wymiarach 25×65mm, której wzór ścieżek oraz schemat montażowy przedstawia rysunek 6.

Na płytce znajduje się pewna liczba elementów montowanych powierzchniowo (SMD) i to od nich polecam rozpocząć lutowanie. Pozostałe elementy (potencjometr P1, kondensator C5, złącza J1… J3 oraz JP1) są montowane po tej samej stronie, a wybór kolejności lutowania jest podyktowany wyłącznie własnymi preferencjami.

Prawidłowo zmontowany układ jest od razu gotowy do działa. Nie wymaga jakichkolwiek czynności uruchomieniowych poza ustawieniem żądanej długości impulsu wyjściowego za pomocą potencjometru P1. Stopień podziału częstotliwości jest wybierany poprzez nałożenie zworki na odpowiednią parę wyprowadzeń złącza JP1, zgodnie z ich opisem na płytce.

Zasilanie (podłączane do zacisków złącza J3) powinno odbywać się napięciem stałym i dobrze fi ltrowanym, choć niekoniecznie stabilizowanym. Dopuszczalny zakres jego wartości jest taki sam, jak dla układów serii CD4xxx, czyli od 3V do 18V. Pobierany prąd silnie zależy od aktywności układu: w stanie spoczynku (brak impulsów wejściowych) wynosi kilka mikroamperów, a podczas odliczania wzrasta do kilku miliamperów, zależnie od częstotliwości i napięcia zasilającego.

Impulsy wchodzące do układu (za pośrednictwem zacisków złącza J1) nie mają narzuconych wymagań dotyczących czasu narastania ani opadania, ponieważ wejście zegarowe układu CD4017 jest opatrzone przerzutnikiem Schmitta.

Wydajność prądowa wyjścia układu jest niewielka i zależy od temperatury oraz napięcia zasilającego. W temperaturze 25ºC, przy napięciu 5V wynosi ok. 1mA, a przy 15V ok. 6,8mA (wartości typowe, zaczerpnięte z noty Texas Instruments). Długość impulsu wyjściowego można zwiększyć poprzez wymianę potencjometru P1 na egzemplarz o większej rezystancji ścieżki oporowej, np. 100kΩ. Nie zalecam przy tym znacznego zwiększania pojemności C2, ponieważ przełoży się to na wydłużenie czasu martwego przerzutnika.