SPI

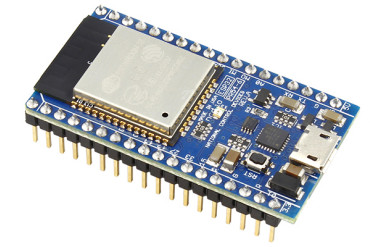

Nieskomplikowanym, a jednocześnie bardzo szybkim interfejsem szeregowym, działającym w sposób synchroniczny, jest SPI (ang. Serial Peripheral Interface). Interfejs ten jest przeznaczony do przesyłania danych na krótkie odległości, zwykle pomiędzy mikrokontrolerami a układami peryferyjnymi, w obrębie jednego systemu wbudowanego. SPI korzysta z architektury master-slave, w której urządzenie nadrzędne (master) koordynuje komunikację z jednym lub większą liczbą urządzeń podrzędnych (slave), sterując sygnałami zegara i wyboru układu. W zależności od konfiguracji SPI może działać w trybie full-duplex lub half-duplex.

Interfejs SPI zawiera cztery charakterystyczne linie sygnałowe:

- MOSI (Master Out Slave In) – linia umożliwiająca urządzeniu master wysyłanie danych do slave’a, czasami oznaczana jako SDI w urządzeniu slave,

- MISO (Master In Slave Out) – linia umożliwiająca urządzeniom podrzędnym wysyłanie danych do urządzenia nadrzędnego, czasami oznaczana jako SDO w urządzeniu slave,

- SCLK (Serial Clock) – sygnał zegara taktującego transmisję, czasami oznaczany jako SCK,

- SS (Slave Select) – linia umożliwiająca urządzeniu nadrzędnemu wybranie urządzenia podrzędnego, do którego mają zostać wysłane dane. Czasami oznaczana jako CS w urządzeniu slave.

Wiele urządzeń z interfejsem SPI

Interfejs SPI może komunikować się z wieloma urządzeniami podrzędnymi w konfiguracji standardowej (multidrop) lub szeregowej/łańcuchowej (daisy chain).

W konfiguracji multidrop do każdego układu slave doprowadzony jest niezależny sygnał aktywujący SS, a układ master wybiera tylko jeden z układów podrzędnych w danej chwili. Pozostałe linie – MOSI, MISO i SCLK – są współdzielone przez wszystkie dołączone układy. Ponieważ wyprowadzenia MISO urządzeń podrzędnych są ze sobą połączone, muszą być wyjściami trójstanowymi, czyli normalnie działają w trybie wysokiej impedancji i nie oddziałują na magistralę, a gdy urządzenie zostanie wybrane, przełączają się w tryb wyjścia cyfrowego (push-pull).

Niektóre układy slave wyposażone w interfejs SPI mogą być połączone w konfiguracji szeregowej, w której wyjście pierwszego układu slave (MISO) jest połączone z wejściem kolejnego układu slave (MOSI) i analogicznie wygląda połączenie kolejnych układów podrzędnych. Wyjście danych (MISO) ostatniego układu slave trafia do wejścia urządzenia master. Taki układ pracy można porównać do połączenia rejestrów szeregowych w jeden dłuższy łańcuch. Dane z wejścia łańcucha przemierzają cyklicznie każde jego ogniwo, zatem odbiorca danych musi być zdefiniowany w treści ramki. W konfiguracji szeregowej wymagana jest tylko jedna linia SS, która aktywuje cały łańcuch urządzeń.

Transmisja danych

Komunikacja poprzez SPI rozpoczyna się, gdy urządzenie master ustawi stan aktywny na wybranym wyjściu SS – zwykle jest to logiczne 0. Następnie w kolejnych okresach sygnału zegarowego wystawiane są kolejne bity danych na wyjście MOSI. Interfejs SPI może działać w trybie full-duplex, zatem zarówno urządzenie master, jak i slave mogą wysyłać dane w tym samym czasie za pośrednictwem linii MOSI i MISO.

Sygnał zegarowy na linii SCLK synchronizuje przesuwanie i próbkowanie danych, więc prędkość przesyłania informacji jest określana przez częstotliwość sygnału zegarowego. Interfejs SPI pozwala na skonfigurowanie polaryzacji sygnału zegarowego (CPOL), czyli poziomu logicznego w stanie bezczynności oraz jego fazy (CPHA), czyli zbocza, na którym będzie wykonywane próbkowanie. Kombinacje polaryzacji i fazy zegara określają tzw. tryb SPI (SPI Mode).