Symetryczne architektury wieloprocesorowe (ang. symmetric multiprocessing, SMP) zapewniają co prawda elastyczność uruchamiania rozbudowanych systemów operacyjnych, lecz często nie są w stanie zagwarantować deterministycznej wydajności wymaganej przez systemy czasu rzeczywistego. Natomiast asymetryczna architektura wieloprocesorowa (Asymmetric Multiprocessing, AMP) umożliwia optymalizację pod kątem konkretnych zadań poprzez izolowanie obciążeń na odrębnych jednostkach przetwarzających – podejście to może być jednak bardziej złożone we wdrożeniu. Aby sprostać temu wyzwaniu, firma Microchip wykorzystała sprawdzony klaster sprzętowych wątków RISC-V („hartów” w terminologii RISC-V) w ramach pojedynczego zespołu rdzeni (coreplex), tworząc architekturę układową obsługującą funkcjonalność AMP w szerokim zakresie zastosowań przemysłowych oraz aplikacji przetwarzania brzegowego z użyciem AI.

Procesor PIC64GX MPU integruje rdzeń zdolny do uruchomienia systemu Linux z wieloma hartami (wątkami sprzętowymi) w ramach jednego kompleksu, spójnego z podsystemem pamięci. Umożliwia to połączenie deterministycznych systemów czasu rzeczywistego z systemem Linux w jednym klastrze CPU. Takie rozwiązanie pozwala na działanie w trybie AMP w typowych przemysłowych zastosowaniach wizyjnych i brzegowych systemach AI, upraszczając tworzenie oprogramowania mogącego działać na systemach operacyjnych czasu rzeczywistego, Linuksie, a nawet bez systemu operacyjnego (tzw. bare metal).

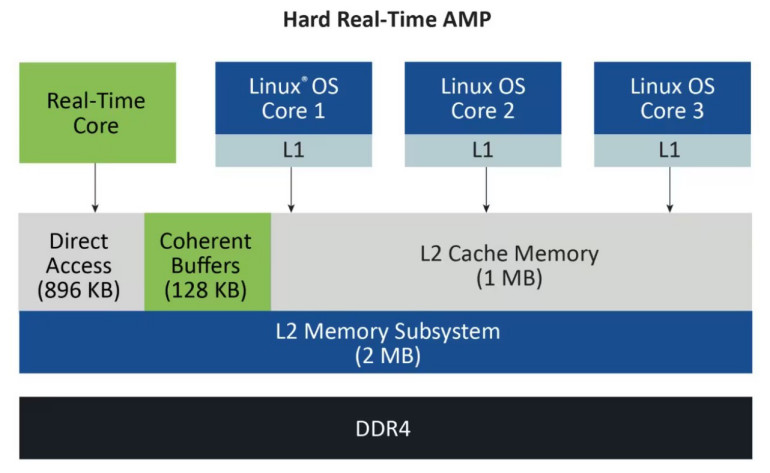

W systemach sterowania i przetwarzania czasu rzeczywistego architektura AMP pozwala programistom przypisać dedykowane jednostki przetwarzające do zadań wrażliwych czasowo, zapewniając przewidywalną wydajność i niskie opóźnienia. Planowanie procesów w Linuksie z zasady nie jest deterministyczne – opóźnienia przerwań potrafią być znaczne i nieprzewidywalne. Dzięki AMP obciążenia wymagające twardych ograniczeń czasowych mogą być obsługiwane przez system RTOS na wydzielonym rdzeniu, podczas gdy funkcje aplikacyjne działają równolegle na Linuksie na innym rdzeniu.

Choć mechanizmy pamięci podręcznej zwiększają wydajność, to nieprzewidywalne problemy z pamięcią cache (tzw. cache misses) mogą powodować wahania czasów wykonania zadań (jitter), co prowadzi do utraty deterministycznego charakteru pracy systemu. Mikroprocesor PIC64GX zapobiega temu, pozwalając kontekstom czasu rzeczywistego działać w trybie Loosely Integrated Memory (LIM), omijając tym samym niedeterministyczne opóźnienia związane z pamięcią cache. Umożliwia to realizację wydajnych potoków przetwarzania, szczególnie w przypadku obciążeń algorytmami AI i uczenia maszynowego, minimalizując czasy przetwarzania.

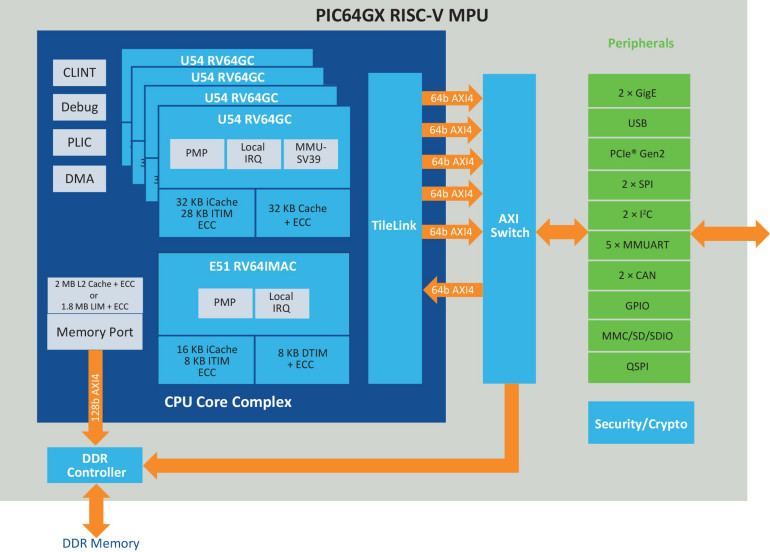

System bazuje na 64-bitowym rdzeniu RV64IMAC E51, taktowanym zegarem 600 MHz i pełniącym rolę monitora systemu. Jest on wyposażony w 16 kB pamięci, którą można skonfigurować jako 2-drożną pamięć podręczną instrukcji L1 z korekcją błędów lub jako ściśle zintegrowaną pamięć instrukcji, a także 8 kB ściśle zintegrowanej pamięci danych i jednostkę PMP (Physical Memory Protection) do obsługi aplikacji.

Sercem układu jest jednak kompleks czterech 64-bitowych hartów aplikacyjnych U54 RV64GC, z maksymalną częstotliwością pracy 600 MHz, z których każdy zapewnia wydajność rzędu 3,1 CoreMark/MHz i 1,7 DMIPS/MHz. Jest to klaster znany z układów SoC z serii PolarFire, co stanowi gwarancję niezawodnego, sprawdzonego podsystemu wielordzeniowego oraz ugruntowanego ekosystemu narzędzi. Piąty hart (E51) zarządza funkcjami monitorującymi układu, lecz jest również dostępny do bezpośredniego uruchamiania zadań czasu rzeczywistego lub bare-metal, jeśli zajdzie taka potrzeba.

Subsystem pamięci L1 obejmuje 32 kB 8-drożnej pamięci podręcznej instrukcji (lub opcjonalnie 28 kB ściśle zintegrowanej pamięci instrukcji) oraz 32 kB 8-drożnej pamięci podręcznej danych. Dodatkowo przewidziano jednostkę ochrony pamięci PMP oraz jednostkę zarządzania pamięcią (MMU). Podsystem pamięci oferuje wiele funkcji, w tym 2 MB pamięci L2 z różnymi trybami dostępu, zintegrowany kontroler pamięci obsługujący różne wersje DDR, jednostkę ochrony pamięci MPU i wbudowaną nieulotną pamięć zapewniającą opcje bezpiecznego bootowania.

Spójna z cache matryca połączeń (bus matrix) CPU oraz elastyczny, 2-megabajtowy podsystem pamięci L2 odgrywają kluczową rolę w działaniu trybu AMP. Pamięć z korekcją błędów można skonfigurować jako 16-drożną pamięć podręczną L2 lub w trybie Loosely Integrated Memory (LIM) dla deterministycznego dostępu, a także jako spójną pamięć typu Scratchpad do obsługi współdzielonych komunikatów między hartami.

Zintegrowany 36-bitowy kontroler pamięci DDR4/LPDDR4 z korekcją błędów obsługuje pamięci DDR4 o przepustowości 1,6 Gb/s i oferuje przestrzeń adresową 8 GB. Kontroler zawiera jednostkę ochrony pamięci (MPU) oraz wbudowaną pamięć nieulotną 128 kB (eNVM) do obsługi procesu bootowania. Takie rozwiązanie zapewnia w pełni elastyczną konfigurację startową, umożliwiając podział hartów przy uruchomieniu – na te pracujące w trybie czasu rzeczywistego oraz te uruchamiające Linuksa – z odpowiednim wsparciem cache L2.

Implementacja AMP

W architekturze RISC-V jednostki przetwarzające określa się jako wątki sprzętowe (harts). Każdy hart w układzie PIC64GX stanowi niezależny kontekst wykonawczy, zdolny do uruchomienia własnego systemu operacyjnego lub zadania typu bare-metal. Czterohartowy klaster aplikacyjny można skonfigurować do pracy maksymalnie w dwóch niezależnych kontekstach programowych. Każdemu z kontekstów można przypisać własny system operacyjny, wydzielone obszary pamięci oraz zasoby sprzętowe. Sprzętowe mechanizmy separacji uniemożliwiają jednemu kontekstowi dostęp do zasobów innego. Wszelkie naruszenia mogą zostać wykryte i obsłużone przez oprogramowanie Hart Software Services (HSS), a hart E51 (monitor) jest przeznaczony do uruchamiania firmware HSS.

HSS pełni rolę bootloadera zerowego poziomu (zero-stage), monitora systemowego oraz dostawcy usług wykonawczych dla aplikacji. HSS wspomaga wczesną inicjalizację systemu – w tym trening kontrolera DDR oraz konfigurację/inicjalizację sprzętu. Kod HSS w większości wykonuje się na rdzeniu E51, z niewielką częścią funkcjonalności działającą w trybie maszynowym na każdym z rdzeni U54. HSS uruchamia jeden lub więcej kontekstów, ładując kod aplikacji z pamięci startowej (którą może być wbudowana pamięć NVM) i zapewnia środowisko wykonawcze platformy/nadzorcy (Platform Runtime Services/Supervisor Execution Environment, SEE) dla jąder systemów operacyjnych. Wspiera także bezpieczny rozruch (secure boot) i jest istotnym elementem gwarantującym sprzętową separację kontekstów w środowisku AMP.

Za pomocą HSS konfigurowany jest czterohartowy kompleks rdzeni. Na przykład możliwe jest ustawienie trzech hartów U54 do uruchamiania systemu Linux i instalacja systemu operacyjnego czasu rzeczywistego Zephyr na pozostałym, czwartym harcie. Peryferia sprzętowe mogą zostać przypisane do jednego lub drugiego z tych kontekstów.

Otwarty, standardowy framework programistyczny o nazwie Open Asymmetric Multiprocessing (OpenAMP) dostarcza komponenty programowe niezbędne do tworzenia aplikacji dla systemów AMP. Kluczowymi elementami OpenAMP są mechanizmy Remote Processor Messaging (RPMsg) oraz remote Processor (remoteProc), które umożliwiają podział zadań pomiędzy dwa konteksty AMP i łatwą komunikację między nimi.

Wskazówki projektowe

Architektura AMP sprzyja tworzeniu zaawansowanych projektów składających się z wielu współpracujących komponentów programowych. Dzięki sprzętowemu podziałowi zasobów, AMP pozwala pogodzić wymagania i ograniczenia systemów o mieszanej krytyczności z zachowaniem wymogów czasu rzeczywistego.

Programiści powinni zwrócić szczególną uwagę na mapę pamięci i rozmieszczenie pamięci w układach PIC64GX, metody komunikacji RPMsg i RPMsg-Lite, a także własność zasobów – rozumianą jako wyłączne przydzielenie określonych obszarów pamięci i/lub peryferiów do danego kontekstu.

Aplikacje muszą dysponować przejrzystym kanałem komunikacyjnym pomiędzy kontekstami (wykorzystującym RPMsg i współdzieloną pamięć) wraz z jasnym zdefiniowaniem znaczenia przesyłanych komunikatów. Należy dokonać podziału zadań, tak aby efektywnie rozproszyć obciążenia na części możliwe do wydajnego wykonania przez różne jednostki przetwarzające. Każdy hart musi dysponować wystarczającymi zasobami pamięci, a transfer danych między hartami powinien być minimalny – taka konfiguracja redukuje opóźnienia komunikacyjne i maksymalizuje równoległość przetwarzania wątków. HSS pełni funkcję monitora systemowego, raportując błędy magistrali, błędy ECC oraz krytyczne wyjątki występujące na rdzeniach U54.

Peryferia

Pod względem urządzeń peryferyjnych, rodzina procesorów wielohartowych PIC64GX obejmuje zintegrowane interfejsy, m.in. kontrolery Gigabit Ethernet MAC do szybkiej komunikacji, a także USB 2.0 OTG oraz interfejsy kart pamięci SD/SDIO 5.1. Dostępne są dwa porty CAN 2.0, pięć programowalnych portów UART, dwa interfejsy SPI i dwa I²C, a ponadto kontroler pamięci Flash Quad SPI z funkcją wykonywania kodu bezpośrednio z pamięci (execute-in-place) oraz zintegrowany, jedno- lub czteroliniowy port PCIe Gen2 (×1 lub ×4) w trybie Root Port.

Bezpieczeństwo

Różnorodne funkcje bezpieczeństwa zostały zintegrowane w systemie, aby zapewnić solidną ochronę przed zagrożeniami. Podwójne, zintegrowane układy typu PUF (Physically Unclonable Function) stanowią podstawę technologii root of trust dla kluczy szyfrujących, oferując 56 kB bezpiecznej, nieulotnej pamięci sNVM oraz 128 kB wbudowanej, nieulotnej pamięci eNVM – przy czym wszystko jest zintegrowane w ramach jednego chipu. Projekt układu zawiera także wbudowane detektory manipulacji (tamper) i mechanizmy zapobiegawcze, funkcje kontroli integralności dla bloków pamięci sNVM i eNVM oraz zabezpieczenia przed atakami wykorzystującymi różnicową analizę mocy (DPA), które mogą posłużyć do przechwytywania kluczy.

Zastosowania

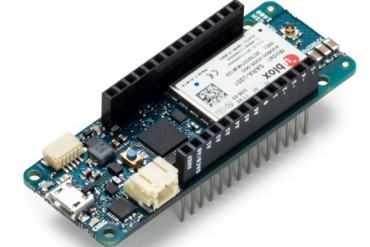

Układy PIC64GX MPU są przeznaczone do zastosowań takich jak jednopłytkowe systemy wbudowane, sterowniki silników, systemy przetwarzania danych w czasie rzeczywistym, systemy wizyjne oraz aplikacje z zakresu AI/ML. Przykładowo, mogą one posłużyć do agregacji danych z czujników i wnioskowania AI poprzez uruchomienie systemu operacyjnego czasu rzeczywistego w pojedynczym kontekście.

Czujniki można z łatwością podłączyć do układu PIC64GX, korzystając z dostępnych peryferiów, takich jak SPI czy I²C. System operacyjny czasu rzeczywistego może następnie przetwarzać dane z czujników, a bloki komunikacyjne – na przykład interfejsy UART lub CAN – mogą posłużyć do transmisji danych (surowych lub przetworzonych), w zależności od potrzeb danego systemu.

W zadaniach z zakresu komputerowego przetwarzania obrazu na poziomie urządzenia brzegowego, odrębny kontekst z systemem Linux może realizować wykrywanie i klasyfikację obiektów oraz strumieniowanie wideo przez interfejsy takie jak Ethernet – wszystko w ramach jednego układu scalonego dzięki możliwościom architektury AMP. W ten sposób można tworzyć mniejsze i bardziej opłacalne rozwiązania w aplikacjach przemysłowych lub medycznych.

Narzędzia

Zastosowanie architektury AMP w przemysłowych aplikacjach SI jest zadaniem o rosnącej złożoności. Mikroprocesor PIC64GX dysponuje jednak kompletnym łańcuchem narzędzi programistycznych, obejmującym toolchain dla Linuksa oraz otwartoźródłowych systemów RTOS, a także wsparcie dla środowisk takich jak VxWorks i innych, używanych w systemach typu safety-critical. Rozszerzenia MPLAB zapewniają możliwość konfiguracji oraz ułatwiają migrację z innych procesorów Microchip. W skład narzędzi wchodzi również pakiet Hart Software Services (HSS), który dostarcza kod źródłowy zeropoziomowego bootloadera HSS oraz monitora systemowego.

Układ ma oficjalne wsparcie (upstream) w ekosystemie systemu operacyjnego Zephyr RTOS oraz w pakiecie BSP (Board Support Package) systemu Linux w ramach Yocto Project. System budowania Linuksa oparty na Buildroot korzysta z jądra Linux4Microchip, a od wersji 2024.10 dostępne jest także wsparcie dla systemu Ubuntu. Pakiet narzędzi zawiera wszystkie sterowniki – w tym sterowniki interfejsów peryferyjnych – niezbędne do rozpoczęcia pracy z układem. Po więcej informacji na temat narzędzi i ekosystemu warto odwiedzić repozytorium GitHub pod adresem https://github.com/pic64gx.

Klaster hartów PIC64GX jest częścią ugruntowanego ekosystemu Mi-V, który obejmuje m.in. wsparcie narzędzi debugujących firm Lauterbach i Ashling. Układ obsługuje funkcje debugowania przez interfejs JTAG – dostępnych jest dziesięć sprzętowych wyzwalaczy na każdy CPU, konfigurowanych jako punkty przerwania (breakpoints) lub punkty obserwacji (watchpoints), a także liczniki wydajności.

Podsumowanie

Układy PIC64GX zostały zaprojektowane specjalnie z myślą o implementacji architektury AMP w inteligentnych aplikacjach brzegowych osadzonych w systemach wbudowanych, które wymagają obsługi zadań o różnej krytyczności. Sprawdzony, wydajny klaster czterech 64-bitowych hartów RISC-V w ramach jednego zespołu rdzeni (coreplex) można bezpiecznie skonfigurować podczas uruchamiania systemu tak, by równolegle uruchomić system operacyjny czasu rzeczywistego obok systemu Linux. Umożliwia to w szczególności stworzenie usprawnionego potoku przetwarzania wizji z wykorzystaniem AI, działającego w czasie rzeczywistym. Dzięki dojrzałemu i dobrze wspieranemu zestawowi narzędzi, mikroprocesor PIC64GX daje deweloperom systemów wbudowanych możliwość pewnego tworzenia złożonych aplikacji przemysłowych, AI/ML oraz systemów czasu rzeczywistego, co usprawnia proces rozwoju i przyspiesza wprowadzanie produktów na rynek.