- ograniczanie napińôcia wyjŇõciowego do¬†ustalonej wartoŇõci,

- pŇāynna regulacja wartoŇõci maksymalnej napińôcia wyjŇõciowego w¬†zakresie 2,5‚Ķ27,5¬†V,

- minimalne napińôcie wejŇõciowe 8¬†V,

- maksymalne napińôcie wejŇõciowe 30¬†V.

PrzykŇāadem zastosowania ukŇāadu jest podŇāńÖczenie stosunkowo delikatnego urzńÖdzenia, np. routera, zasilanego nominalnie napińôciem 12 V, do instalacji samochodowej. Jak wiadomo, napińôcie w instalacji moŇľe dochodzińá do 15 V, a to moŇľe uszkodzińá wspomniane urzńÖdzenie. UŇľycie typowego stabilizatora wymuszaŇāoby utrzymywanie akumulatora w stanie caŇākowitego naŇāadowania, aby zagwarantowańá prawidŇāowy spadek napińôcia na stabilizatorze. Nic sińô jednak nie stanie, jeŇľeli napińôcie spadŇāoby do np. 11,5 V, bo producent urzńÖdzenia na pewno uwzglńôdniŇā tolerancjńô ‚Äěw d√≥Ňā‚ÄĚ, zwińÖzanńÖ z rozrzutami parametr√≥w zasilaczy wtyczkowych.

Prezentowany ukŇāad to stabilizator LDO, ale zaprojektowany do tego, by pracowaŇā prawidŇāowo r√≥wnieŇľ w sytuacji, kiedy napińôcie wejŇõciowe jest mniejsze niŇľ to, kt√≥re uŇľytkownik zadaŇā potencjometrem. Jedynym ograniczeniem minimalnego napińôcia wejŇõciowego jest jego zdolnoŇõńá do prawidŇāowego otwarcia tranzystora MOSFET, o czym dalej.

Budowa i dziaŇāanie

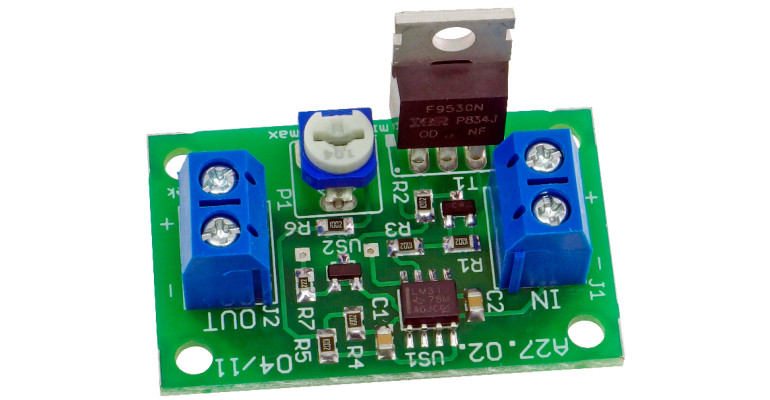

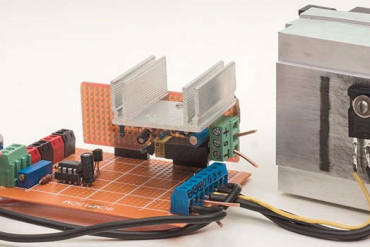

Elementem wykonawczym, przez kt√≥ry pŇāynie prńÖd zasilajńÖcy odbiornik, jest tranzystor T2 typu MOSFET-P. Jednak nie zostaŇā uŇľyty w roli wt√≥rnika, jak zwykle ma to miejsce w stabilizatorach liniowych, lecz obcińÖŇľenie jest wŇāńÖczone mińôdzy jego dren i masńô ukŇāadu. Zatem jest to konfiguracja wsp√≥lnego Ňļr√≥dŇāa, cechujńÖca sińô tym, Ňľe odwraca fazńô. Jednak ma pewnńÖ istotnńÖ zaletńô: potencjaŇā bramki, czyli elektrody sterujńÖcej, musi byńá niŇľszy od potencjaŇāu Ňļr√≥dŇāa, czyli od napińôcia wejŇõciowego. Zatem do peŇānego otwarcia kanaŇāu tranzystora, kiedy prezentuje on sobńÖ rezystancjńô zaledwie 300 mő©, nie potrzeba napińôcia wyŇľszego niŇľ zasilajńÖce ‚Äď wystarczy zewrzeńá bramkńô z masńÖ. PodnoszńÖc potencjaŇā bramki, moŇľna ograniczańá prńÖd pŇāynńÖcy przez tranzystor i tym samym zmniejszańá napińôcie wyjŇõciowe.

Kiedy tranzystor T1 jest zatkany, przez jego kolektor nie pŇāynie prńÖd, wińôc bramka T2 jest polaryzowana potencjaŇāem 0 V, czyli moŇľe byńá silnie otwarty. WycińÖgajńÖc z bazy T1 niewielki prńÖd, moŇľna podnieŇõńá potencjaŇā bramki T2 dzińôki temu, Ňľe T1 ‚Äědolewa‚ÄĚ prńÖdu do rezystora R2. RolńÖ R1 jest utrzymywanie T1 w stanie zatkania wtedy, kiedy nie musi on przewodzińá. Maksymalne napińôcia bramka-Ňļr√≥dŇāo uŇľytego w prototypie tranzystora T2 to 20 V. Dioda D1 zapobiega przebiciu izolacji podbramkowej tego tranzystora, ograniczajńÖc napińôcie bramka-Ňļr√≥dŇāo do ‚Äď15 V. To wystarczy, aby w peŇāni otworzyńá ten tranzystor, a jednoczeŇõnie pozostawia pewien margines bezpieczeŇĄstwa.

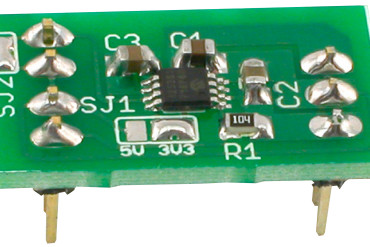

Za sterowanie bazńÖ T1 odpowiada komparator LM311. Jednak zostaŇā uŇľyty w roli elementu liniowego: jego wejŇõciowy ukŇāad r√≥Ňľnicowy tworzy wzmacniacz bŇāńôdu, a wyjŇõciowy tranzystor NPN ‚Äěwsysa‚ÄĚ prńÖd kolektorem z bazy T1. Zatem LM311 zostaŇā potraktowany jako ukŇāad r√≥Ňľnicowy z gotowymi Ňļr√≥dŇāami prńÖdowymi do jego polaryzacji, przez co caŇāy ukŇāad ogranicznika jest prostszy, niŇľ gdyby taki obw√≥d budowańá od zera, z tranzystor√≥w dyskretnych. UkŇāad US1 otrzymuje dwie wielkoŇõci wejŇõciowe. JednńÖ z nich jest napińôcie wyjŇõciowe, podzielone przez dzielnik rezystancyjny R4, P1. DrugńÖ z nich jest napińôcie referencyjne o wartoŇõci 2,5 V, kt√≥rego dostarcza scalone Ňļr√≥dŇāo typu TL431. Rezystory R5 i R6 zapewniajńÖ jego prawidŇāowńÖ polaryzacjńô w caŇāym dopuszczalnym zakresie napińôcia zasilania. Ich r√≥wnolegŇāe poŇāńÖczenie ma sens wtedy, kiedy to napińôcie jest wysokie, aby nie przekroczyńá maksymalnej mocy traconej na pojedynczym elemencie.

JednoczeŇõnie ich rezystancja wypadkowa zostaŇāa tak dobrana, aby Ňļr√≥dŇāo napińôcia referencyjnego US2 pracowaŇāo poprawnie w caŇāym dopuszczalnym zakresie napińôcia wejŇõciowego. Kondensator C1 jest wŇāńÖczony blisko wyprowadzeŇĄ zasilania ukŇāadu US1, aby zapobiegańá jego wzbudzeniu i filtrowańá zasilanie z szybkozmiennych zakŇā√≥ceŇĄ szpilkowych.