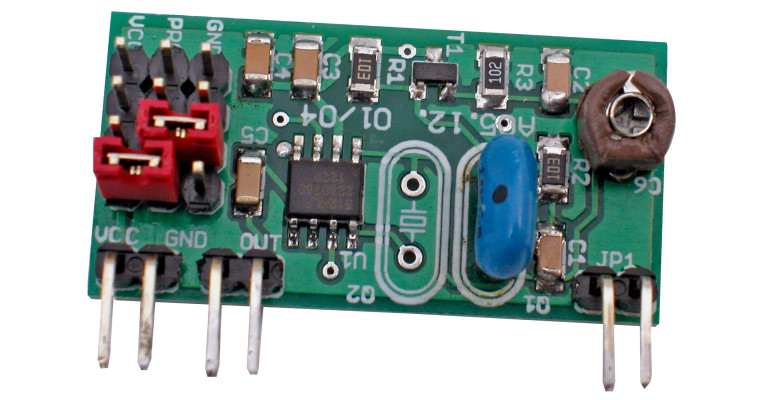

Głównym elementem opisywanego generatora jest układ powielacza (mnożnika) częstotliwości ICS512, który do powielania częstotliwości wykorzystuje pętlę fazową PLL (Phase-Locked-Loop). Jest to prosty i tani sposób generowania sygnałów wysokiej częstotliwości LOCO (Low Cost Oscillator) zastępujący oscylator w wielu systemach elektronicznych. Bardzo prosta aplikacja z minimalną liczbą elementów zewnętrznych, pozwala na powielanie częstotliwości zegarowej ×2, ×2,5, ×3, ×3, ×3,333, ×4, ×5, ×5,333, ×6, ×8 zarówno z rezonatora kwarcowego (układ ma wbudowany generator), jak i z generatora zewnętrznego. Wyjście układu jest buforowane, a sygnał wyjściowy charakteryzuje się małym jitterem (50 ps), szybkim narostem (1 ns) i dobrą symetrią (typowo 49…51%).

Współczynniki mnożenia można programować zależnie od potrzeby poprzez wybór konfiguracji poziomów logicznych na wyprowadzeniach 6 i 7 (sygnały S0 i S1). Na wyjściu CLK (pin 5) uzyskuje się sygnał o poziomie logicznym CMOS z odpowiednio powieloną częstotliwością wejściową.

ICS512 jest przewidziany do pracy w rozszerzonym zakresie temperatur (-40 do +85 C) i jest zamykany w obudowie SOIC 8 pin (rzadziej występuje w innych obudowach). Układ może współpracować z rezonatorem kwarcowym o częstotliwości od 5 do 27 MHz, a przy doprowadzeniu sygnału z zewnętrznego źródła, jego częstotliwość może zawierać się w zakresie od 2…50 MHz. Według danych katalogowych maksymalna częstotliwość wyjściowa układu wynosi 200 MHz, a napięcie zasilania 3…5,5 V ze średnim poborem prądu 20 mA).