Układ SSD1306 ma możliwość komunikowania się z systemem nadrzędnym za pomocą magistrali równoległej w standardzie Intel 8080 lub Motorola 6800 oraz za pomocą interfejsu szeregowego SPI lub I²C. Dla aplikacji, w których jest ważna prędkość transmisji danych jest wybierana któraś z magistrali równoległych, a w pozostałych wypadkach – magistrale szeregowe. Dla wielu typowych aplikacji jest wystarczająca prędkość transmisji dostępna za pomocą interfejsu szeregowego.

Aktywny interfejs jest wybierany sprzętowo przez wymuszenie poziomów logicznych na wejściach konfiguracyjnych BS0…BS2.

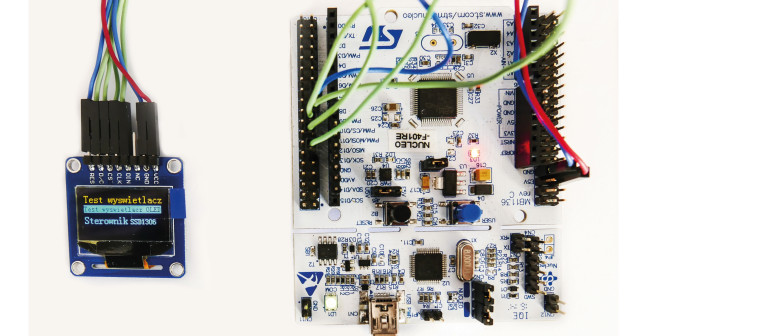

Poziom na wejściu BS2 określa czy będzie użyty interfejs szeregowy (BS2=0), czy równoległy (BS2=1). W tym wyświetlaczu BS2 jest na stałe dołączony do masy i mamy możliwość wyboru tylko jednego z trzech interfejsów szeregowych. Na płytce drukowanej wyświetlacza są umieszczone dwa pola lutownicze umożliwiające ustawianie poziomów na BS0 i BS1. Fabrycznie są tam wymuszone poziomy BS0=0 i BS1=0, czyli 4-przewodowy interfejs SPI. Zgodnie z tym ustawieniem są opisane wyprowadzenia płytki wyświetlacza. Oczywiście, można zmienić interfejs, ale nie widziałem powodu, aby to robić w układzie testowym, więc pozostawiłem ustawienia fabryczne

Ponieważ nie przewidziano odczytywania jakichkolwiek danych ze sterownika, to SPI ma tylko linię danych DIN (MOSI z punktu widzenia hosta) oraz linię zegarową CLK. Oprócz tych linii, do przesyłania danych jest używana linia CS i D/C.

Wejście CS jest standardowym sygnałem SPI uaktywniającym układ, do którego są wysyłane dane. Wykorzystując CS można do jednej magistrali dołączyć kilka wyświetlaczy – każdy wybierany za pomocą odrębnej linii CS. Linia D/C jest wykorzystywana do kierowania danych albo do rejestru komend (D/C=0), albo do pamięci obrazu (D/C=1). Przy 3-przewodowym interfejsie SPI brak jest sygnału D/C i jest konieczne przesłanie dodatkowego bitu informującego sterownik, gdzie maja trafić dane z magistrali. Komplikuje to obsługę transmisji, bo dane są 9-bitowe i nie można wykorzystać standardowych, sprzętowych interfejsów SPI wysyłających słowa 1-bajtowe. Używając interfejs I²C trzeba dodatkowo wysłać po adresie slave bajt kontrolny. Z jednej strony dodatkowa linia D/C wymaga linii portu sterownika, a z drugiej strony jej użycie przyśpiesza i upraszcza transfer danych.

Pamięć obrazu GDDRAM (Graphic Dispaly Data)

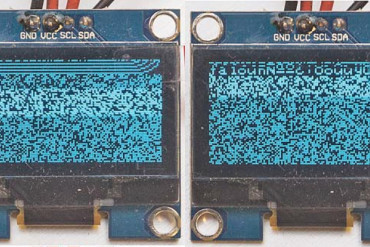

Pamięć obrazu jest statyczną pamięcią RAM o organizacji 128×64 bity. Każdemu bitowi pamięci odpowiada pojedynczy piksel na matrycy OLED. Pamięć o takiej organizacji nie może być bezpośrednio zapisywana przez mikrokontroler, dlatego została logicznie podzielona na 8 stron (Page0….Page7). Jedna strona zawiera 128 bajtów. Zapisanie bajtu do pamięci odpowiada pionowej linijce o długości 8 pikseli. Aby zapewnić elastyczność przy mechanicznym mocowaniu wyświetlacza jest możliwe remapowanie segmentów: są one wybierane licząc od lewej do prawej, od 127 do 0. Podobnie są remapowane linie matrycy. Remapowaniem sterują dwie komendy: Set Segment Re-map (A0/A1) i Set COM Output Scan Direction (C0/C8).

Zapisywanie danych do pamięci RAM jest adresowane przez dwa liczniki adresowe: licznik kolumn zmieniający się w zakresie 0…127 i licznik stron zmieniający się w zakresie 0…7. Dostęp do pamięci RAM powoduje automatyczne zwiększenie licznika kolumn i/lub licznika stron. Zakres zmiany adresów i sposób inkrementacji jest określany przez tryb adresowania ustawiany komendą Set Memory Addressing (20h).