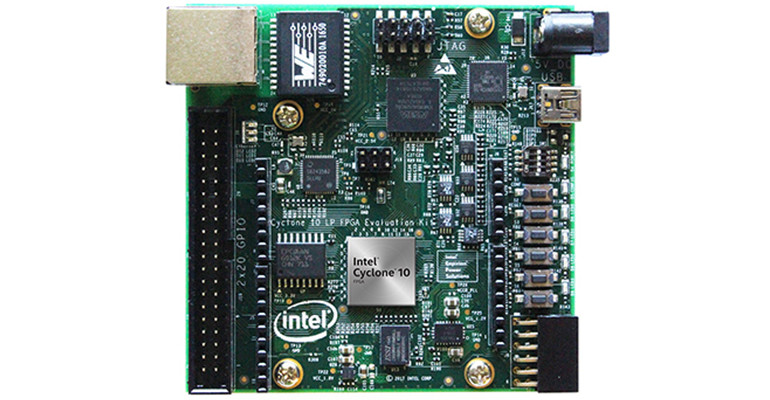

Jest to płytka przeznaczona do tworzenia nieskomplikowanych rozwiązań, m.in. bramek logicznych i prostszych kontrolerów na podstawie układu FPGA rodziny Cyclone 10 LP firmy Intel wyposażonego w 25 tysięcy programowalnych bloków logicznych, która posiada niedużą liczbę peryferii w postaci przycisków, przełączników DIP i diod LED, a także:

- wydajną pamięć HyperRAM 128 MB o przepustowości 100 MB/s, obsługiwaną przez gotowy w użyciu blok HMBC (HyperBus Memory Controller) firmy Synaptic Labs,

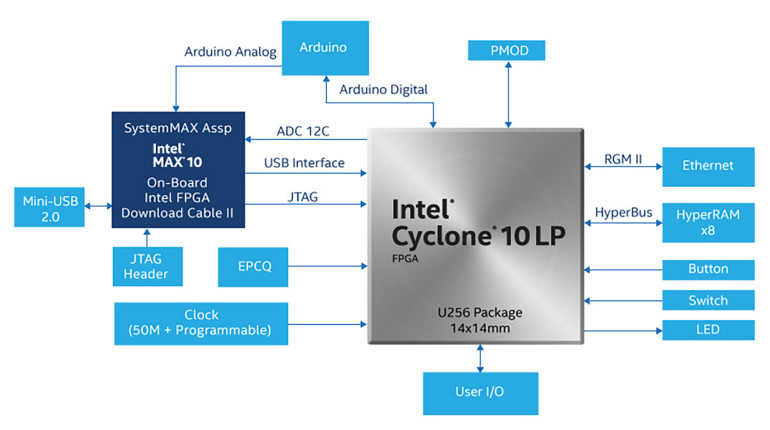

- oparty na układzie FPGA rodziny MAX10 kontroler SystemMAX pełniący rolę:

- sterownika USB-Blaster II,

- układu zarządzającego sygnałami zegarowymi,

- układu monitorującego prądy i napięcia na wyprowadzeniach układu FPGA rodziny Cyclone 10 LP.

Wszystko to pojedynczym interfejsie Ethernet, 4 zegarach i złączach: GPIO, Pmod oraz Arduino do bezproblemowego podłączania modułów i zestawów, wliczając moduły shield. Obsługę zestawu zapewnia środowisko Quartus firmy Intel wraz z dokumentacją elektroniczną na stronie producenta. Zakres jego projektów jest przy tym ograniczony tylko wyobraźnią twórcy. Jest to produkt polecany w szczególności osobom ceniących minimalizm rozwiązań. Obecność kabla USB jest w Cyclone 10 LP FPGA Evaluation Kit wliczona (bez zasilacza).

Specyfikacja zestawu Cyclone 10 LP FPGA Evaluation Kit:

- Układ FPGA rodziny Cyclone 10 LP o oznaczeniu 10CL025YU256I7G:

- 24624 programowalnych bloków logicznych

- 594 kbit pamięci RAM

- 4 pętle PLL

- 150 wyprowadzeń I/O

- Programowanie przez:

- port USB

- sterownik USB-Blaster II

- złącze JTAG

- układ EPCQ64

- Wbudowany kontroler SystemMAX:

- Układ FPGA rodziny MAX10 o oznaczeniu 10M08SAU169C8G

- Sterownik USB-Blaster II (rozwiązanie Embedded Intel FPGA Download Cable II)

- Możliwość zarządzania sygnałami zegarowymi

- Obsługa wejść analogowych złącza Arduino w oparciu o dziewięciokanałowy przetwornik analogowo-cyfrowy

- Możliwość pomiaru prądów i napięć na wyprowadzeniach układu FPGA z rodziny Cyclone 10 LP

- Pamięć HyperRAM:

- Pojemność: 128 Mb

- 8-bitowa magistrala danych

- Przepustowość danych: 100 MB/s

- Obsługa w oparciu o blok HMBC (HyperBus Memory Controller) firmy Synaptic Labs w środowisku Intel Quartus Prime Lite

- Interfejs Ethernet:

- Gniazdo RJ-45

- Układ XWAY PHY11G PEF 7071 firmy Intel,

- Przepływności: 10 Mb/s, 100 Mb/s i 1 Gb/s

- Magistrala RGMII (dla układu FPGA z rodziny Cyclone 10 LP)

- Zegary:

- 50 MHz - 2 szt.:

- Ogólnego przeznaczenia

- Dla pamięci HyperRAM

- 125 MHz - 1 szt.:

- Dla interfejsu Ethernet

- O konfigurowalnej częstotliwości - 1 szt.:

- Ogólnego przeznaczenia

- 50 MHz - 2 szt.:

- Peryferia:

- Diody LED:

- Użytkownika (koloru zielonego) - 4 szt.

- Zasilania (koloru niebieskiego) - 1 szt.

- Konfiguracji układu FPGA (koloru żółtego) - 1 szt.

- Przyciski:

- Użytkownika - 4 szt.

- Resetu konfiguracji układu FPGA - 1 szt.

- Rekonfiguracji układu FPGA - 1 szt.

- Przełączniki DIP:

- Użytkownika - 3 szt.

- Do obsługi funkcji Virtual JTAG Tap - 1 szt.

- Diody LED:

- Złącza:

- GPIO o 40 wyprowadzeniach - 2 szt.

- Pmod - 1 szt.

- Arduino - 1 szt.

- Zasilanie:

- Z kabla USB (złącze mini-USB współdzielone ze sterownikiem USB-Blaster II)

- Z zewnątrz (5 V)

- Zastosowane układy:

- Przetwornica Enpirion EP5358LUI firmy Intel o prądzie wyjściowym 600 mA

- Przetwornica Enpirion EN5329QI firmy Intel o prądzie wyjściowym 2 A

- Przetwornica Enpirion EN5339QI firmy Intel o prądzie wyjściowym 3 A

Środowisko Intel Quartus Prime Lite (narzędzie darmowe - zalecana wersja możliwe najnowsza, uwzględniająca rodzinę Cyclone 10 LP układów FPGA)