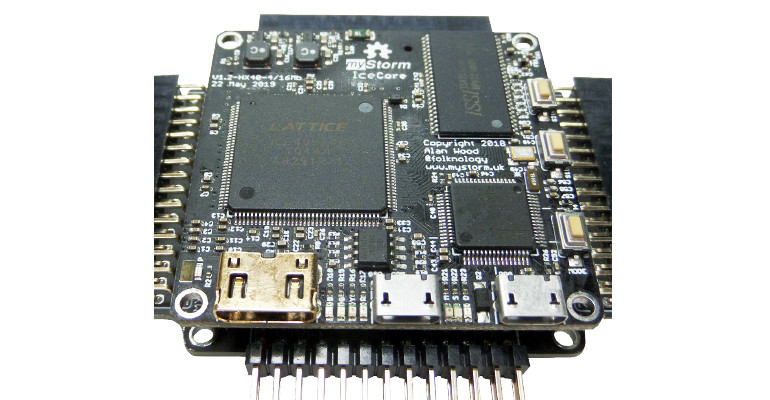

Na rynku istnieje wiele rozwiązań dla rodziny układów Lattice, jednak jeśli chcemy pozostać wierni idei otwartego oprogramowania, najlepszym wyborem będzie zakup urządzenia, którego dokumentacja jest dostępna na licencji Open Hardware. Jednym z takich rozwiązań jest płytka ICECore ICE40 HX, do której jest dostępna pełna dokumentacja projektowa. Można ją nabyć w cenie około 50 USD (tindie.com), co wydaje się stosunkowo atrakcyjną ceną, gdy nie planujemy zajmować się własnoręcznym wykonaniem płytki na podstawie dostępnej dokumentacji.

Za wyborem tego rozwiązania przemawia również fakt, że w skład zestawu wchodzi nie tylko sam układ ICE40, ale również dodatkowy mikrokontroler STM32F730 taktowany zegarem 200 MHz, który jest połączony z FPGA za pomocą dwóch magistral SPI. Dodatkowo do dyspozycji mamy pamięć SDRAM oraz FLASH-SPI, co umożliwia tworzenie zaawansowanych rozwiązań, jak na przykład implementacja własnych układów SOC.

Budowa płytki IceCore ICE40 HX

Zestaw uruchomieniowy ICE core jest jednym z tańszych zestawów ewaluacyjnych, którego dokumentacja dostępna jest na otwartej licencji Open Hardware. Charakteryzuje się następującymi parametrami:

- bazuje na układzie FPGA Lattice HX4K zawierającym 4000 bloków LUT oraz 80 kb pamięci Block RAM,

- zawiera mikrokontroler STM32F730 mający 256 kB pamięci RAM oraz 64 kB pamięci FLASH,

- pamięć SDRAM 16 Mbit (2 MB) o maksymalnej częstotliwości 143 MHz,

- pamięć FLASH 16 MBit (2 MB) o maksymalnej częstotliwości pracy 100 MHz,

- złącze karty SD,

- 4 diody LED oraz 2 przyciski,

- dwa złącza micro USB, w tym jedno przeznaczone do programowania oraz konfiguracji,

- dodatkowe cztery złącza zewnętrzne dołączone zarówno do mikrokontrolera, jak i układu FPGA.

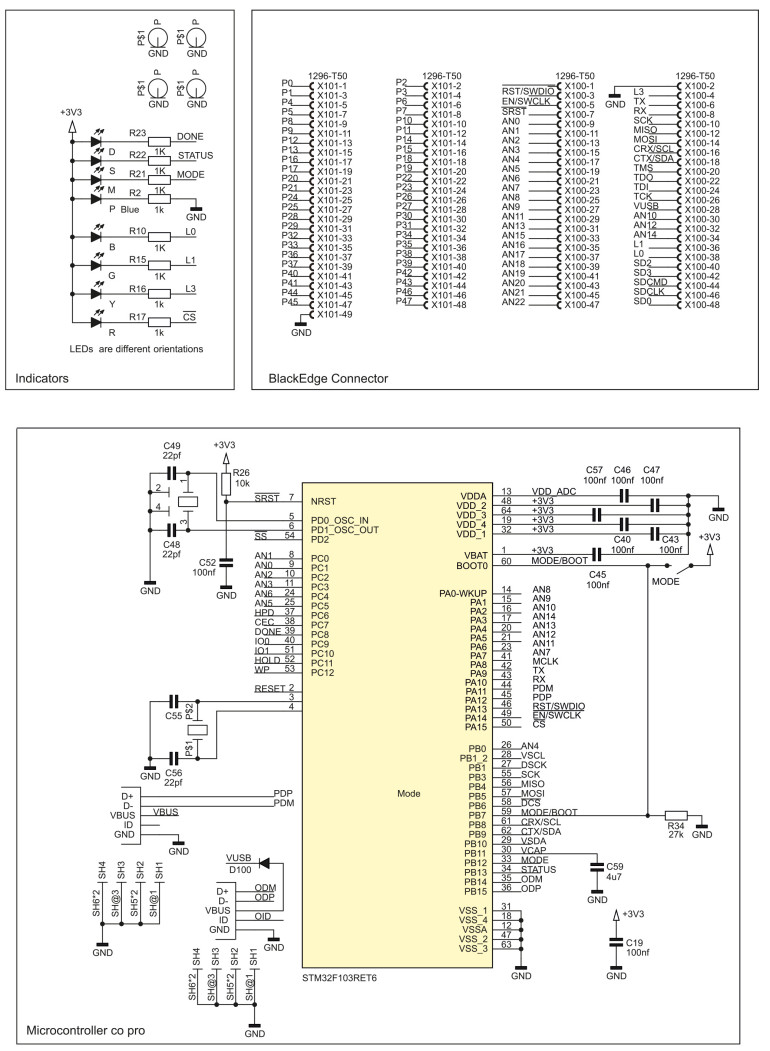

Schemat ideowy zestawu został pokazany na rysunku 1. Zasilanie doprowadzane jest bezpośrednio z portu USB za pomocą złączy USB-COM lub USB-PRG. Napięcie z portu USB po odfiltrowaniu podawane jest na dwa stabilizatory impulsowe dostarczające napięć 1,2 V do zasilania rdzenia FPGA (Vcc) oraz 3,3 V do zasilania części IO FPGA i mikrokontrolera. Napięcie 3,3 V po podaniu przez dodatkowy filtr RC jest również podawane do części analogowej układu IC2.

Istotną funkcję w zestawie pełni mikrokontroler STM32F730 (IC2), połączony jest z układem programowalnym za pomocą dwóch magistral SPI. Magistrala dołączona do linii 73...75 układu FPGA przeznaczona jest do ogólnej komunikacji pomiędzy układem FPGA i mikrokontrolerem. Natomiast magistrala dołączona do linii 63, 64, 67, 68, 70, 71, które stanowią wejście sprzętowego kontrolera SPI, pełni potrójną funkcję. Jej głównym zadaniem jest konfigurowanie FPGA przez mikrokontroler (linia wyboru CS (56)), po przesłaniu pliku konfiguracyjnego z portu USB-PROG przez komputer. Drugą funkcją magistrali jest dostęp do pamięci SPI-FLASH, która aktywowana jest za pomocą linii wyboru CS1 (55). Trzecią funkcją jest dostęp do pamięci SERIAL-FLASH, FPGA oraz mikrokontrolera za pomocą złącza zewnętrznego (COMS/DBG). Ponieważ pamięć dostępna jest zarówno z mikrokontrolera, jak i FPGA, może być używana przez oba układy.