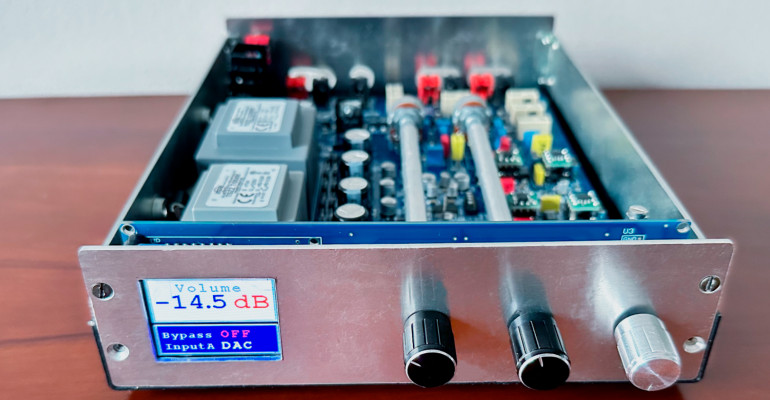

- regulator poziomu zrealizowany na znanym i od wielu lat produkowanym układzie PGA2320 firmy Texas Instruments,

- aktywny układ regulacji tonów niskich i tonów wysokich z możliwością jego całkowitego ominięcia (bypass),

- selektor wejść z 3 wejściami stereofonicznymi przełączanymi miniaturowymi przekaźnikami sygnałowymi,

- zbudowany na bazie wzmacniaczy operacyjnych zoptymalizowanych do zastosowań audio,

- zawiera przetwornik cyfrowo-analogowy na bazie stosunkowo taniego i bardzo dobrego układu PCM1794A.

Przetwornik analogowo-cyfrowy

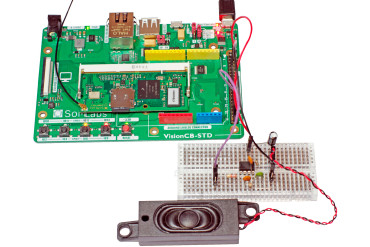

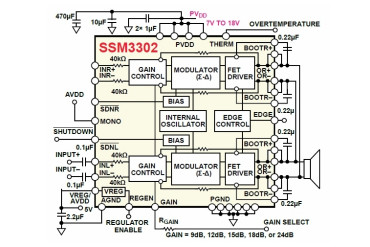

Układ przetwornika analogowo-cyfrowego jest zbudowany na bazie scalonego przetwornika PCM1794A wraz z układami zasilającymi, układu konwertera prąd/napięcie oraz układu rekonstruującego filtra dolnoprzepustowego. Oprócz układu przetwornika umieszczono tu też odbiornik S/PDIF i złącze do podłączenia interfejsu USB/I²S.

Parametry PCM1794A są bardzo dobre:

- zakres dynamiki 127 dB dla sygnału stereo,

- zniekształcenia THD+N 0,0004%,

- rozdzielczość 24 bity,

- zaawansowany moduł konwertera cyfra/prąd,

- 8-krotne nadpróbkowanie we wbudowanym filtrze,

- częstotliwość próbkowania sygnału wejściowego od 10 kHz do 200 kHz,

- wyjście prądowe 7,8 mApp,

- interfejs danych wejściowych w formatach I²S, left justified,

- wydzielone wyprowadzenia masy i zasilania części cyfrowej +3,3 V (linie interfejsu akceptują poziomy +5 V) i części analogowej +5 V.

Dane z interfejsu szeregowego są 8-krotnie nadpróbkowane w cyfrowym filtrze dolnoprzepustowym. Pozwala to uprościć analogowy dolnoprzepustowy filtr rekonstruujący, ponieważ może mieć szersze pasmo przepustowe i łagodną charakterystykę opadania.

PCM1794A nie ma szeregowego interfejsu pozwalającego na zapisanie ustawień i ewentualną cyfrową regulację poziomu sygnału przez mikrokontroler - host. Wszystkie możliwe konfiguracje są wykonywane przez wymuszanie stanów logicznych na wejściach konfiguracyjnych układu.

Cyfrowe dane audio są przesyłane 3-przewodowym interfejsem audio w formatach wybieranych przez stany wymuszane na wejściach FMT0 i FMT. Obecnie praktycznie używa się tylko formatu I²S i taki tu został na stałe ustawiony przez wymuszenie stanów niskich na FMT0 i FMT1. Wykonuje się to poprzez zwarcie pinów 5...6 i 7...8 w złączu konfiguracyjnym P12.

Synchroniczna magistrala danych audio jest zbudowana z trzech linii:

- linii danych (wejście DATA),

- linii identyfikacji kanałów stereo (wejście LRCK),

- linii zegarowej taktującej przesyłaniem danych (wejście BCK).

Częstotliwość na linii BCK jest 64 razy wyższa od częstotliwości LRCK. Dodatkowo przetwornik wymaga sygnału zegarowego MCLK (master Clock) o częstotliwości będącej standardową wielokrotnością zegara BCK. Wszystkie sygnały zegarowe: LRCK, BCK i MCLK, muszą być zgodne fazowo.

Sygnały z magistrali danych są przesyłane ze złącza P11 przez rezystory szeregowe R65, R68, R70, R71 o wartości 27 Ω. Złącze P11 umożliwia przełączanie za pomocą zworek sygnałów I²S z dwu źródeł: odbiornika S/PDIF DIR9001 - układ U15 lub konwertera USB/I²S z wyprowadzeniami w standardzie Amanero podłączanego do złącza P7. Konwerter również może generować sygnał zegara systemowego MCLK. Pierwotnie przewidywałem przełączanie tych sygnałów za pomocą dwu przekaźników, ale ostatecznie zrezygnowałem z tego pomysłu, żeby nie komplikować i tak rozbudowanego układu.

Zwarcie wyprowadzeń 1...2 złącza P12 powoduje wyciszenie wyjść analogowych przetwornika (MUTE), kiedy układy przetwornika nie wykryją cyfrowych danych audio. Zwarcie pinów 3...4 powoduje wyłączenie układu deemfazy przetwornika (zalecane).

Przetwornik jest zasilany napięciem +5 V w sekcji analogowej i +3,3 V w sekcji cyfrowej. Sekcja analogowa jest zasilana z trzech oddzielnych zasilaczy parametrycznych opartych na układzie TL431. To stosunkowo proste układowe rozwiązanie dostarcza osobnych napięć VCC2L, VCC2R i VCC. W założeniu ma to poprawić pracę sekcji analogowej przetwornika. Źródłem napięcia wejściowego zasilaczy parametrycznych jest stabilizowane przez układ LM317 napięcie +7 V. Napięcie +3,3 V do zasilania układów cyfrowych przetwornika i zasilania odbiornika S/PDIF pochodzi z niskoszumowego stabilizatora U18.

Przetwornik ma wyjście prądowe i do działania niezbędny jest zewnętrzny konwerter prąd-napięcie. Ten konwerter i dolnoprzepustowy filtr rekonstruujący zbudowane są na bazie rozwiązania zaproponowanego w danych katalogowych PCM1794A ze wzmacniaczami operacyjnymi OPA1611 i OPA1612 produkcji TI. Zostało ono przeze mnie wypróbowane w innych konstrukcjach i według mnie działa bardzo dobrze. W konwerterze I/U dla lewego kanału pracuje podwójny wzmacniacz operacyjny OPA1612 (U12). W kanale prawym jest to wzmacniacz U16.

W filtrze dolnoprzepustowym użyłem pojedynczych wzmacniaczy OPA1611 - dla kanału lewego U14, a dla kanału prawego U17. Wzmacniacze są zasilane symetrycznym napięciem ±12 V blokowanym dla każdego z układów parą kondensatorów: elektrolitycznym 10 μF/25 V i ceramicznym 100 nF. Jak już wiemy, wyjścia analogowe przetwornika są podawane na wejście selektora źródeł i dalej przesyłane w torze przedwzmacniacza tak jak inne sygnały wejściowe.

Źródłem cyfrowego sygnału audio dla przetwornika może być odbiornik S/PDIF typu DIR9001. To znany i bardzo dobry odbiornik z niskim jitterem. Maksymalna częstotliwość próbkowania sygnału wejściowego to 96 kHz. Dla zwolenników bardzo "gęstych" formatów to zbyt mało, ale w praktyce dla normalnego dotwarzania zupełnie wystarczy. Odbiornik ma wejście danych S/PDIF w standardzie TTL i dlatego konieczny jest konwerter poziomów ze standardu S/PDIF do TTL wykonany na zlinearyzowanych bramkach 74HCU04 - układ U19.

Wejścia PSCK0 i PSCK1 określają mnożnik częstotliwości zegara systemowego MCLK. Tu mamy ustawioną na stałe wartość fs×256. Dla fs= 44,1 kHz (standard CD) zegar MCLK będzie miał częstotliwość 11,2896 MHz. Wejścia FMT0 i FMT1 ustalają format danych wyjściowych. Jak wiemy, powinien być to I²S, ponieważ taki format danych wejściowych został ustalony w przetworniku PCM1794A.