Wprowadzenie

Zapewnienie zgodności z normami EMC staje się coraz bardziej wymagającym zagadnieniem. Postęp technologiczny pozwolił na zmniejszenie rozmiaru elementów, jednak wykreował on również szczególne wyzwanie, jakim jest kontrolowanie odporności urządzenia na zakłócenia elektromagnetyczne.

Aktualne wymagania dotyczące odporności zwiększają znacznie koszty projektu i produkcji urządzeń. Testując odporność na poziomie komponentów (tj. układów scalonych) można je jednak łatwiej zidentyfikować i podjąć działania zaradcze.

Wyniki testów odporności pozwalają na wstępną selekcję określonych układów scalonych (w tym układów ASIC) do dalszego rozwoju wyrobu. Dodatkowo, mogą one zostać włączone do analizy układów scalonych oraz przyczynić się do optymalizacji komponentów.

Wprawdzie w branży istnieją już procedury testowe, które umożliwiły zgromadzenie bogatego doświadczenia w ocenie odporności układów scalonych, ale koncepcja stojąca za obecną metodą testowania wprowadza tu pewną zmianę. Polega ona na przykładaniu impulsów zakłócających bezpośrednio do pinów testowanych układów scalonych. Kształt i amplituda zastosowanych zakłóceń są specjalnie tak dobrane, aby naśladować typowe zjawiska, na jakie narażony byłby układ scalony podczas standardowego testu odporności urządzenia zawierającego ten układ lub podczas pracy w zakłóconym środowisku.

W czasie pracy sprzęt techniczny, obiekty i urządzenia są zazwyczaj zasilane przez pulsujące sygnały zakłócające. W związku z tym standardowe testy urządzeń symulują na przykład generowanie iskry na styku przełącznika (burst) lub wyładowanie elektrostatyczne (ESD).

W przypadku standardowej metody testowania obserwuje się odporność w trybie aktywnym (tj. zachowanie działających układów scalonych zasilanych napięciem). Kryterium zaliczenia testu stanowi niezakłócone funkcjonowanie układu scalonego.

Wpływy środowiskowe lub sam test mogą powodować powstawanie napięć i prądów znacznie wyższych, niż określone maksymalne wartości dla układów scalonych.

Analiza odporności na poziomie układu scalonego ma tę zaletę, że nie wymaga uwzględnienia wpływu konstrukcji urządzenia na EMC. Obejmuje to na przykład projekt płytki drukowanej, rodzaj i dostępność złącza lub konstrukcję obudowy.

Co więcej, podczas testowania odporności układu scalonego, efekty zakłóceń są mniej wyraźne, niż podczas testowania całego urządzenia – skutkuje to lepszą powtarzalnością wyników testu. W niniejszym artykule opisano połączenie między testem urządzenia, a testem ziarnistości pinów układu scalonego.

Testowanie urządzeń

Ze względu na ciągły wzrost cyfryzacji i powszechne stosowanie podzespołów elektronicznych, wiele urządzeń wymaga wysokiego stopnia odporności. Szczególnie ważne jest przeprowadzanie testów odporności na zakłócenia impulsowe podczas badania obiektów technicznych i urządzeń. Wynika to z faktu, że będą one narażone na zakłócenia impulsowe również podczas pracy i standardowego użytkowania.

Odpowiednie impulsy zakłócające (burst i ESD) w testach odporności opisano w następujących normach: IEC 61000-4-4 „Szybki test odporności na zakłócenia przejściowe (burst)” oraz IEC 61000-4-2 „Odporność na wyładowania elektrostatyczne (ESD)”:

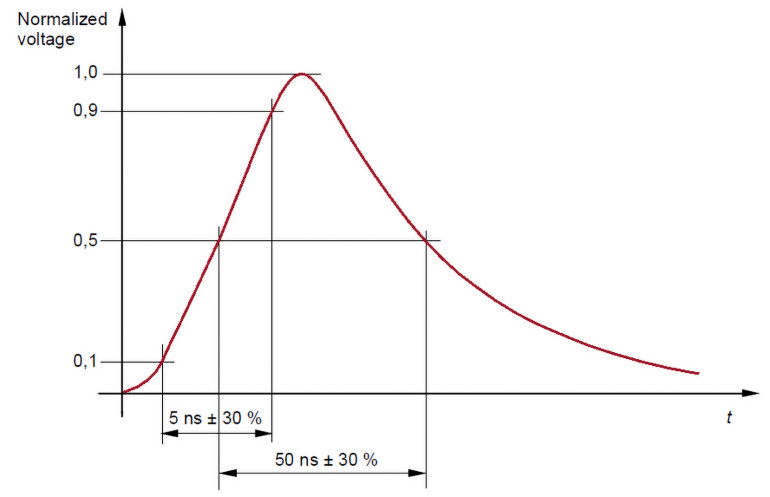

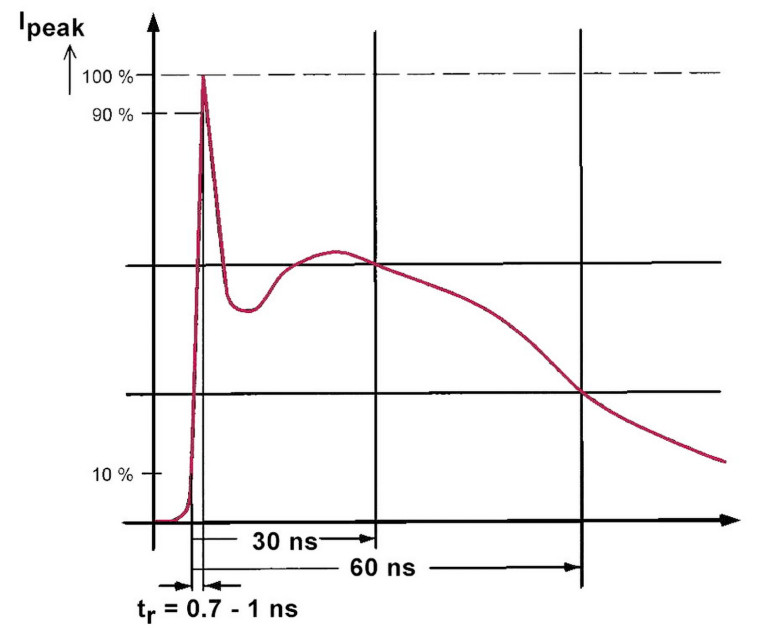

Przy impedancji źródła wynoszącej 50 Ω, do urządzenia przykładane są impulsy o minimalnym napięciu ±2 kV, ze zboczem narastającym trwającym 5 ns i zboczem opadającym trwającym 50 ns (połowa amplitudy – patrz rysunek 1).

To właśnie z tych impulsów składają się impulsy BURST. Przy impedancji źródła wynoszącej 330 Ω do urządzenia przykładane są impulsy o napięciu co najmniej ±6 kV ze zboczem narastającym 0,7 ns i zboczem opadającym 5 ns (połowa amplitudy – rysunek 2).

Podstawowe zasady testowania urządzeń pod kątem zakłóceń

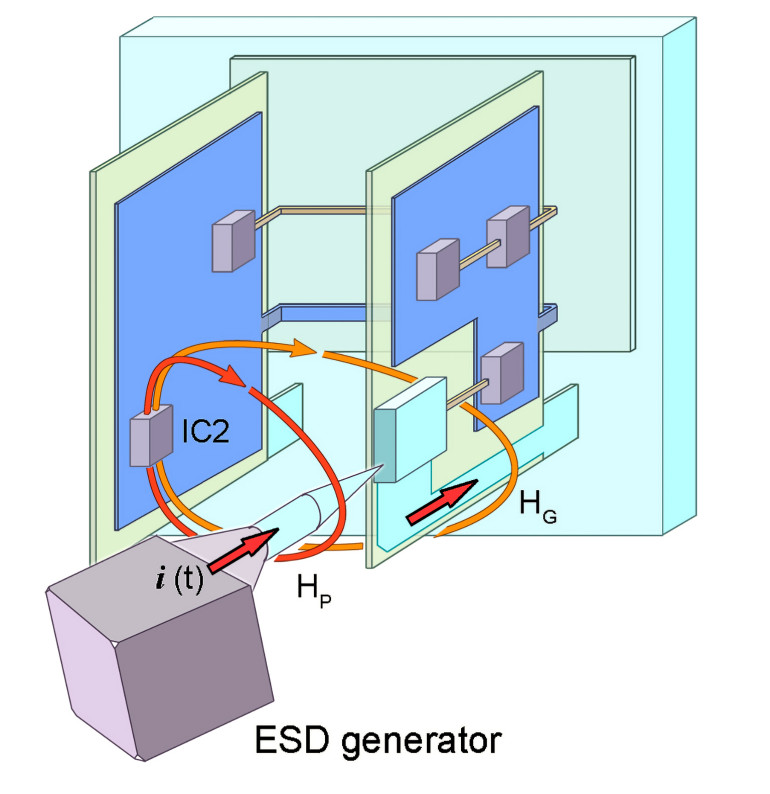

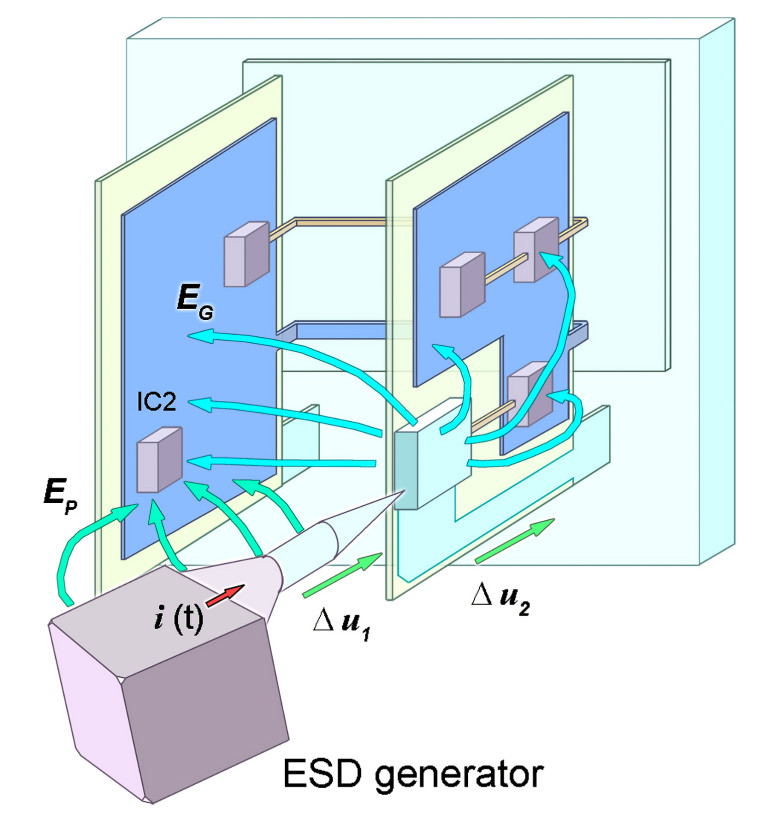

W celu badania odporności, do urządzenia przykładane jest zakłócenie w kształcie impulsu zarówno w jego zamierzonej lokalizacji, jak i niezależnie od niej. Impuls pierwotnego zakłócenia (ESD lub burst) napięcia u(t) przyłożony do urządzenia powoduje przepływ impulsowego prądu zakłócającego i(t) przez urządzenie (rysunek 3). Dwa podstawowe mechanizmy – sprzężenie magnetyczne i sprzężenie pola elektrycznego (pole E) – choć występują jednocześnie, powinny być rozpatrywane indywidualnie.

1. Sprzężenie pola magnetycznego H (indukcyjne)

Interferencja pola magnetycznego H(t) tworzy się wokół przewodnika przenoszącego prąd interferencyjny i(t). Im niższa impedancja obwodu pierwotnego, tym większy przepływ prądu, a tym samym silniejsze pole magnetyczne H.

W idealnym przypadku natężenie pola wokół prostego przewodnika jest określone przez wzór:

Zakłócenia pola magnetycznego przenikają przez urządzenie i otaczające je komponenty oraz przez płytki drukowane. Pętle przewodników znajdują się na płytkach drukowanych lub w komponentach (np. układ scalony, rysunek 3). Zakłócenia pola magnetycznego generują wtórne napięcie zakłócające u_sec(t) na indukcyjności L – patrz wzór:

To napięcie zakłócające potencjalnie występuje na przykład w obwodach wewnętrznych układu scalonego, co może spowodować nieprawidłowości w działaniu tego komponentu.

2. Sprzężenie pola elektrycznego

Podstawowy impuls zakłócający (ESD lub burst) napięcia u(t) przyłożonego do urządzenia powoduje spadek napięcia na zespole (rysunek 4).

Pole elektryczne E(t) uzyskuje się z różnicy napięć wzdłuż obserwowanej geometrii. Im wyższa impedancja pierwotnej ścieżki prądu, tym wyższa różnica napięć, a tym samym wyższe wynikowe pole E. Pole E przenosi zakłócenia jako prąd przesunięcia i(t) w pętlach wtórnych, takich jak kable sygnałowe i/lub styki układu scalonego, poprzez sprzężenie pojemnościowe. Proces zachodzi za pośrednictwem pojemności sprzęgającej C, która mieści się w zakresie fF – patrz wzór.

Napięcie interferencyjne jest wytwarzane na rezystancji wewnętrznej pętli wtórnej przez sprzężony pojemnościowo prąd i(t). To napięcie zakłócające może być obecne na pinie układu scalonego i wyzwalać zakłócenia w jego funkcjonowaniu.

W obu przypadkach (sprzężenie spowodowane przez pole magnetyczne lub pole E), zakłócenie jest zmniejszane o współczynnik jeden (współczynnik urządzenia) podczas przejścia z pierwotnego obwodu zakłócającego do pętli wtórnej i jest zlokalizowane na aktywnym układzie elektronicznym (np. na układzie scalonym). Napięcia zakłócające 6 kV, które zwykle występują podczas testu urządzenia ESD, zmniejszają się do wartości leżącej w przedziale od 0,1 V do kilkuset woltów.

Spadek ten zależy od impedancji w pierwotnym i wtórnym obwodzie zakłócającym.

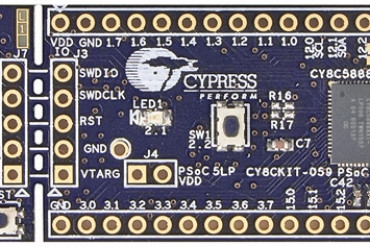

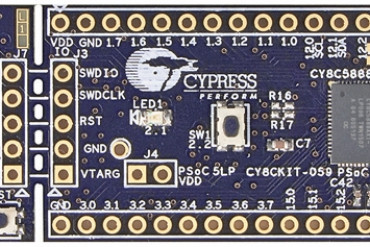

Układy scalone zamontowane na płytce drukowanej są narażone na działanie pól magnetycznych H(t) i elektrycznych E(t).

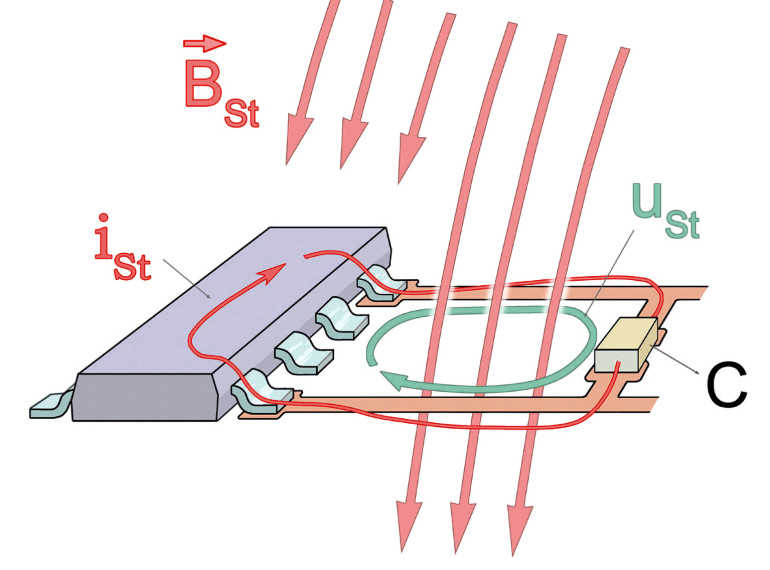

Sprzężenie magnetyczno-polowe (indukcyjne) w układach scalonych

Gęstość strumienia magnetycznego Bst(t) przenika przez najmniejsze pętle przewodnika (np. między układem scalonym a dołączonym kondensatorem odsprzęgającym – rysunek 5).

Napięcie Ust jest indukowane w pętli obwodu przez strumień magnetyczny Φ, jak opisano w:

Napięcie Ust doprowadza prąd zakłócający do układu scalonego. Impedancja tego źródła zakłóceń jest niska ze względu na formowanie się sygnału w pętli przewodnika. Może to prowadzić do powstawania prądów Ist (t) o wysokim natężeniu.

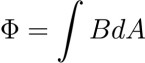

Sprzężenie pola elektrycznego E (pojemnościowe) w układach scalonych

Natężenie pola elektrycznego E(t) lub związany z powierzchnią przewodzącą prąd przemieszczenia D(t) generuje zakłócenia Ist(t) w przewodniku (rysunek 6). Zakłócenia te powodują wzrost napięcia Ust(t) na powierzchni przewodzącej, który może zniekształcać sygnały logiczne przesyłane przez ścieżki. Prąd przesunięcia Ist(t) może również propagować do układów scalonych i wyzwalać dalsze zakłócenia. Źródło zakłóceń „pola elektrycznego” ma wysoką impedancję.

Symulacja

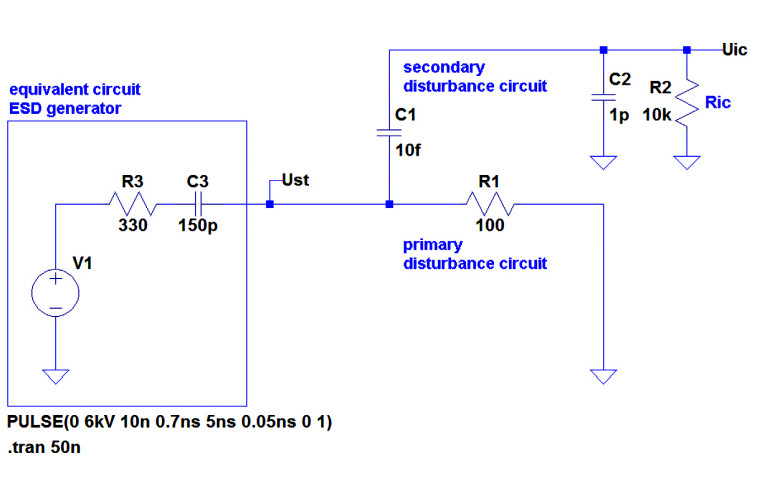

Poniższe symulacje (rysunki 7...11) bazują na pewnych uproszczeniach. Na rysunku 7 generowanie impulsu ESD zostało znacznie uproszczone. Obwód równoważny opiera się na zasadach sprzężenia pojemnościowego, pokazanych na rysunku 4.

Szacowanie napięcia zakłócającego na układzie scalonym

Dodatni impuls zakłócający o amplitudzie 6 kV jest wstrzykiwany jako wyładowanie kontaktowe w pierwotnym obwodzie zakłócającym (rysunek 7).

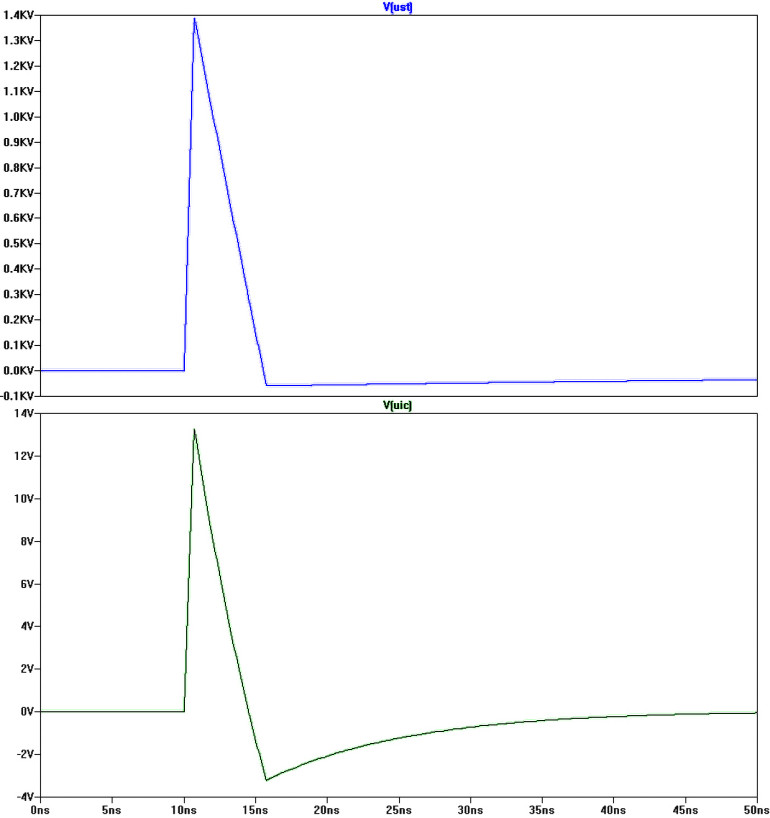

Pik napięcia zakłócającego (Ust) o wartości 1,4 kV powstaje na impedancji pierwotnej R1 (rysunek 8). Napięcie zakłócające 13,5 V pozostaje w kontakcie ze stykiem układu scalonego o wysokiej impedancji poprzez sprzężenie pojemnościowe (sprzężenie pola E) przez C1. Impedancja pierwotnego obwodu zakłócającego może być znacznie większa (1 kΩ), przez co napięcie zakłócające na pinie układu scalonego może przekraczać 100 V, co grozi znacznym przekroczeniem specyfikacji maksymalnych wartości znamionowych układów scalonych.

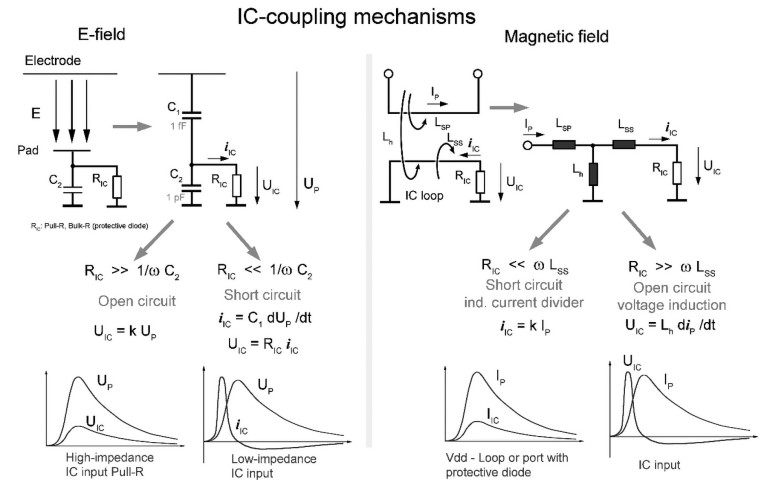

Tryby sprzęgania

Rodzaj sprzężenia zależy również od stosunku impedancji źródła do impedancji obciążenia, tj. do impedancji wejściowej układu scalonego.

Sprzężenie pola elektrycznego E (pojemnościowe)

Przy nachyleniu 1 ns skutkującym maksymalną szybkością transferu 1 GHz zakłada się, że pojemność sprzęgająca C1 wynosi 1 pF. Impedancja X tejże pojemności przyjmuje wtedy wartość 159 Ω. Gdy rezystancja wejściowa układu scalonego wynosi 10 kΩ, jest ona znacznie większa niż rezystancja źródła (impedancja C1). W związku z tym sąsiedni impuls interferencyjny na R2 (na układzie scalonym) ma taki sam kształt fali, jak pierwotny impuls interferencyjny. Powoduje to proporcjonalny podział napięcia z dzielnikiem pojemnościowym C1, C2.

RiIC » XC1

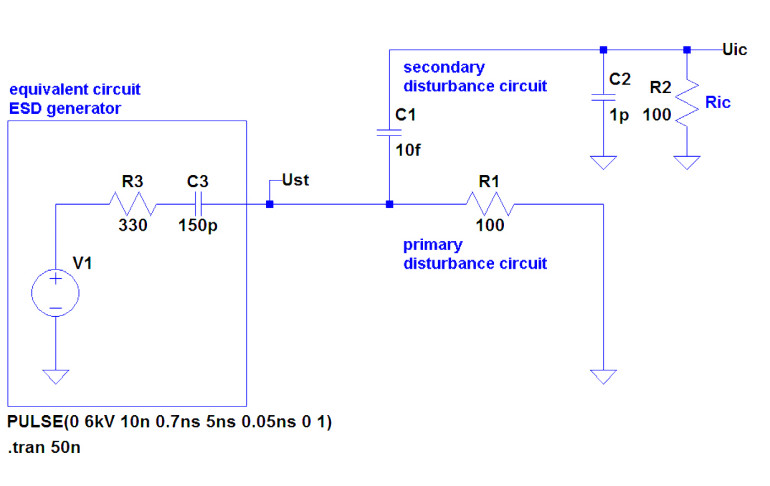

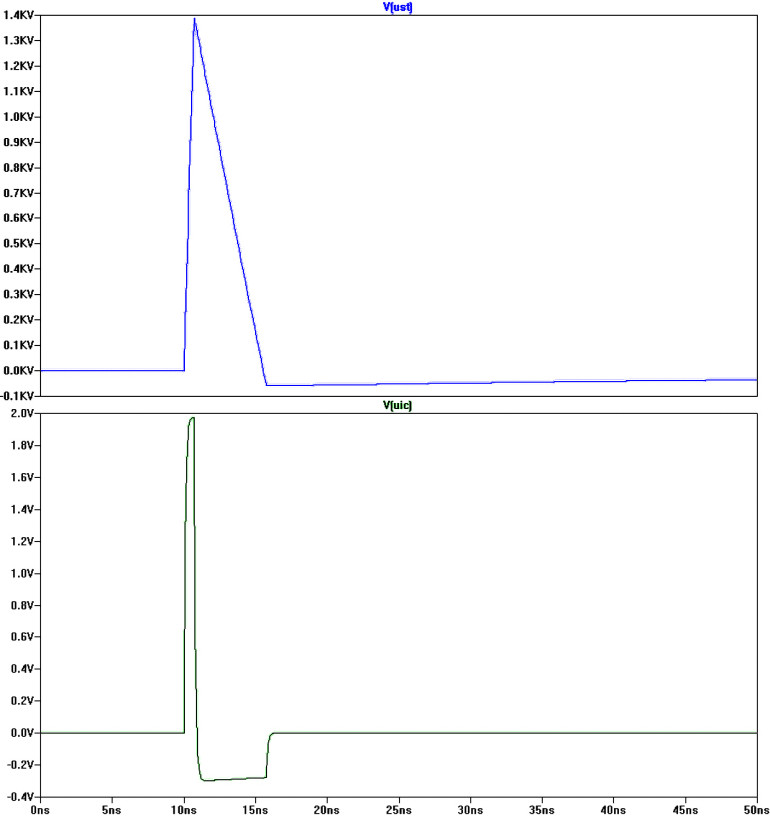

Zupełnie inne warunki uzyskuje się, gdy impedancja obciążenia jest mniejsza niż impedancja źródła. Poniższy przykład zakłada R2=100 Ω, C1=10 fF.

RiIC ‹ XC1

W tych warunkach główny impuls zakłócający jest rozróżniany w układzie scalonym (rysunki 9 i 10).

Sprzężenie pola H (magnetycznego)

W przypadku sprzężenia z polem H warunki są odwrotne. W stanie spoczynku:

- Ric » Xss jest zróżnicowany,

- Ric ‹ Xss jest podzielony prądowo.

Podsumowanie mechanizmów sprzęgania pokazano na rysunku 11.

W przypadku sprzężenia pola H przyjmuje się schemat zastępczy obwodu transformatora z indukcyjnością główną (Lh) oraz indukcyjnością upływu (Ls).