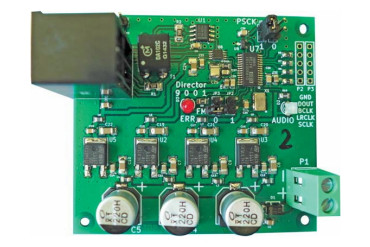

W przypadku korekcji PFC, układ STNRG011A użytkuje reduktory zniekształceń i ogranicznik częstotliwości. Zastosowany został m.in. ośmiobitowy rdzeń nadzorczy z peryferiami, a także nieulotna pamięć, która przechowuje np. dane kalibracyjne oraz konfiguracje układu. Obecny jest interfejs UART przeznaczony do komunikacji i obserwacji pracy STNRG011A. Interfejs ten upraszcza testowanie, zapewniając nadzór w czasie rzeczywistym czy zdalne zarządzanie. To wszystko ma miejsce przy wbudowanym układzie rozładowywania kondensatorów, który jest zgodny z normą IEC 62368-1. Gwarantuje to obniżenie poboru mocy w trybie czuwania. Układ STNRG011A implementuje algorytmy, które korzystają z wewnętrznej pamięci ROM. W chwili, kiedy pracuje zabezpieczenie przed przeciążeniem prądowym, zwiększana jest częstotliwość przełączania, co oprócz utrzymania niezmiennego napięcia na wyjściu, zapobiega wyłączeniu zasilacza. Układ STNRG011A dostępny jest w obudowie SO-20.

Więcej informacji pod adresami: link 1 i link 2 oraz na poniższej dokumentacji.