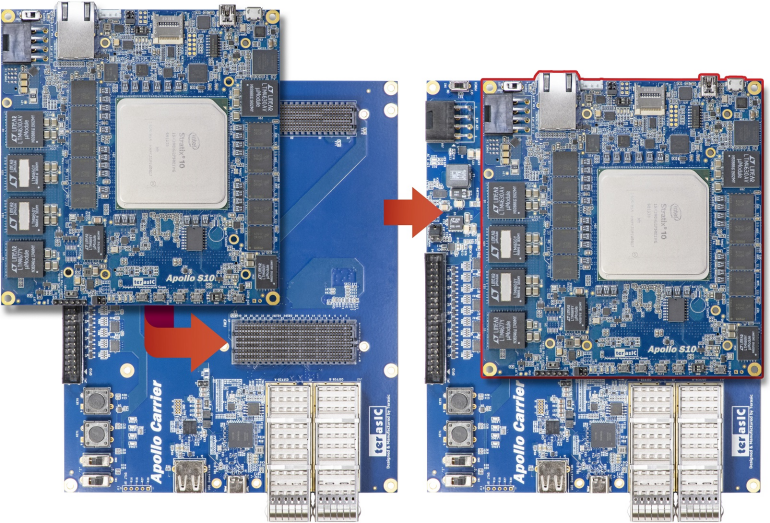

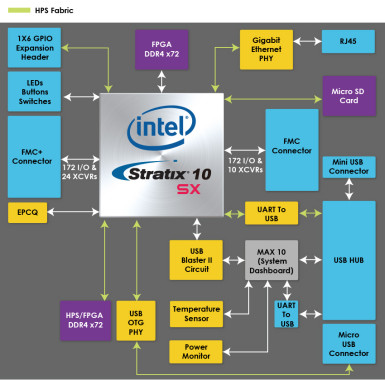

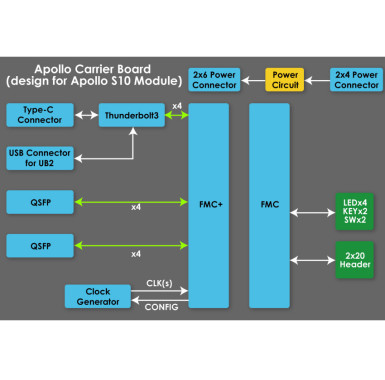

Opracowany przez Terasic moduł obejmuje układ FPGA o oznaczeniu 1SX280HU2F50E1VG. Układ ten jest dedykowany implementacji wielu rozwiązań - w tym celu posiada 2,8 miliona programowalnych bloków logicznych oraz 64-bitowy procesor o 4 rdzeniach i architekturze Cortex-A53 firmy ARM. Dzieje się to przy 2 pamięciach Apollo S10 SoM: DDR4 i QSPI Flash. Występujący w module sterownik USB Blaster II pozwala konfigurować układ FPGA. Moduł zawiera najważniejsze peryferia: diody LED, przyciski, przełączniki DIP, czujnik temperatury, układ RTC oraz 5 gniazd: karty microSD, wentylatora, Gigabit Ethernet (RJ-45), micro-USB i mini-USB. Całość uzupełniają zegary użytkownika o częstotliwościach: 50 MHz i 100 MHz, a także 3 złącza: GPIO, FMC i FMC+, z czego 2 ostatnie są wybierane poprzez złączki. Obsługę modułu zapewnia środowisko Quartus od firmy Intel wraz z dokumentacją elektroniczną na stronie producenta. Moduł Apollo 10 SoM należy stosować wraz z przystawką Apollo Carrier Board (od Terasic). Można do niego dołączać różne rozszerzenia (patrz galeria na końcu).

Specyfikacja modułu Apollo S10 SoM:

- Układ FPGA rodziny Stratix 10 SX (o oznaczeniu 1SX280HU2F50E1VG):

- 2 800 000 programowalnych bloków logicznych

- 229 Mbit pamięci RAM

- 96 transceiverów

- 11 520 układów mnożących

- 5 760 bloków DSP

- 64-bitowy procesor:

- 4 rdzenie

- architektura Cortex-A53 firmy ARM

- Programowanie:

- w oparciu o sterownik USB-Blaster II

- przez pamięć QSPI Flash

- Pamięci:

- DDR4 o pojemności 64 GB i 2 niezależnych bankach

- QSPI Flash o pojemności 1 Gb

- Zegary użytkownika:

- 50 MHz - 4 szt.

- 100 MHz

- Interfejsy:

- Gigabit Ethernet

- UART-USB

- USB OTG

- Peryferia:

- Diody LED - 3 szt.

- Przełączniki DIP - 2 szt.

- Przyciski - 5 szt.

- Czujnik temperatury

- Układ RTC

- Gniazda:

- karty microSD

- micro-USB

- mini-USB

- RJ-45

- wentylatora

- Złącza rozszerzające:

- FMC (Vita57.1) o 10 transceiverach

- FMC+ (Vita57.4) o 24 transceiverach

- GPIO o 6 wyprowadzeniach

- Zasilanie: z zewnątrz (12 V)

Środowisko Intel Quartus Prime Lite (narzędzie darmowe - zalecana wersja możliwe najnowsza, uwzględniająca rodzinę Cyclone IV E układów FPGA)

Dokumentacja Apollo S10 SoM i pozostałe pliki

Więcej informacji pod adresem: terasic.com.tw