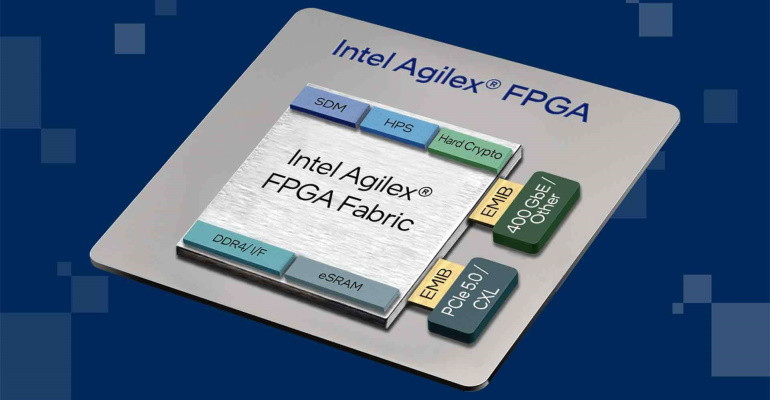

W obliczu wielu ograniczeń: czasowych, budżetowych i energetycznych firmy technologiczne zwracają się do układów FPGA jako elastycznych, programowalnych i wydajnych rozwiązań z sektora elektroniki. Uwzględniający chiplet R-Tile najnowszy układ FPGA z rodziny Agilex 7 z dużą szybkością współpracuje z procesorami Xeon Scalable czwartej generacji. Skalowalna i efektywna w pracy architektura Agilex 7 umożliwia wdrażanie niestandardowych aplikacji na potrzeby m.in. obliczeń wysokiej wydajności. Pozwala to zmniejszyć koszty projektowania dla szybszego wprowadzania rozwiązań na rynek. Dodanie układów FPGA z interfejsem CXL, dla serwerów opartych na procesorach Xeon, przy wykorzystaniu mechanizmu Transparent Page Placement (TPP), znacząco poprawia wydajność działania systemów operacyjnych Linux. Jest to osiągane przy stricte heterogenicznej budowie opisanego układu, która obejmuje chiplety nadawczo-odbiorcze z interfejsami EMIB (ang. Embedded Multi-die Interconnect Bridge).

Serwisy partnerskie:

Użytkownik

Adres e-mail

Status

Aktywny

Kod prenumeratora

Pozostało

Data wygaśnięcia

20-05-2026

Przedłuż

Wyloguj się