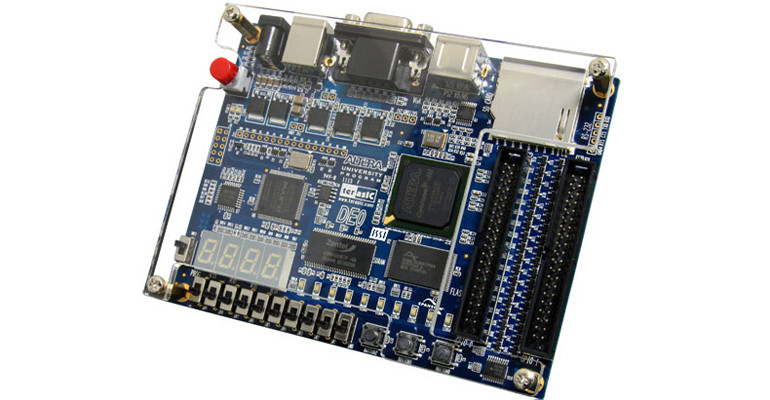

Mowa tu o układzie EP3C16F484 z rodziny Cyclone III, którego pojemność logiczna wynosi 16 tysięcy programowalnych bloków logicznych i jest (w efekcie) idealny dla wielu projektów. Wszystko to przy następujących peryferiach DE0: przyciski, przełączniki, diody LED (o kolorze zielonym), złącze VGA, gniazdo PS/2 (do dołączania klawiatury i myszy) i gniazdo kart microSD. W zestawie występują dwie pamięci: SDRAM o pojemności 8 MB i Flash o pojemności 4 MB, a także dwa złącza rozszerzające: GPIO do podłączania modułów zewnętrznych i innych zestawów, w tym bez układów FPGA (2 szt.) i złącze wyświetlacza LCD 16×2 znaków (wyświetlacz ten nie jest dołączony do DE0). Osoby ceniące minimalizm z pewnością docenią przywołany zestaw. Niski nakład pracy przy dużej wydajności oraz funkcjonalności - to jego zasadnicze cechy, które dopełnia pleksiglasowa płyta w pełni chroniąca DE0 przed upadkami. Obsługę zestawu zapewnia środowisko Quartus i dokumentacja na stronie producenta. Brak przy tym kabla USB oraz zasilacza zewnętrznego w zestawie - poniżej specyfikacja DE0.

Specyfikacja zestawu DE0:

- Układ FPGA rodziny Cyclone III o oznaczeniu EP3C16F484:

- 15408 programowalnych bloków logicznych

- 504000 kbit pamięci RAM

- 56 wbudowanych układów mnożących

- 4 pętle PLL

- 346 wyprowadzeń I/O

- Obudowa BGA o 484 wyprowadzeniach

- Programowanie przez:

- port USB,

- sterownik USB-Blaster (układ EPM240 firmy Altera)

- układ EPCS4

- Pamięci:

- SDRAM o pojemności 8 MB

- Flash o pojemności 4 MB

- Wbudowany zegar 50 MHz

- Interfejs RS-232

- Peryferia:

- Diody LED (kolor zielony) - 10 szt.

- Przełączniki -10 szt.

- Przyciski - 3 szt.

- Czteropozycyjny wyświetlacz siedmiosegmentowy

- Czterobitowe złącze VGA z rezystorowym przetwornikiem drabinkowym (maksymalna rozdzielczość: 1280x1024 px, przy częstotliwości odświeżania równej 60 Hz)

- Gniazdo kart microSD

- Gniazdo PS/2

- Złącze RS232

- Złącza rozszerzające:

- GPIO o 40 wyprowadzeniach - 2 szt.

- wyświetlacza LCD 16×2 znaków

- Zasilanie: z zewnątrz (7,5 V)

- Wymiary: 99,7×128,02 mm

Środowisko Intel Quartus Prime Lite (narzędzie darmowe - zalecana wersja możliwe najnowsza, uwzględniająca rodzinę Cyclone III układów FPGA)

Dokumentacja DE0 i pozostałe pliki

Więcej informacji tutaj oraz na poniższych filmach.