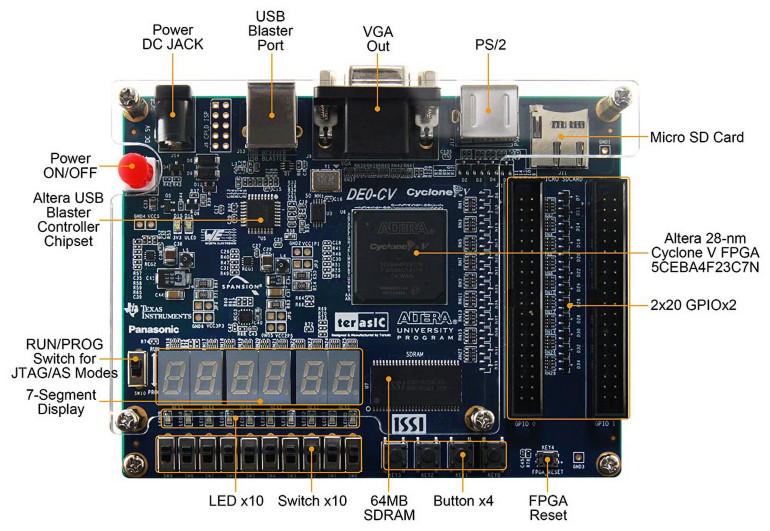

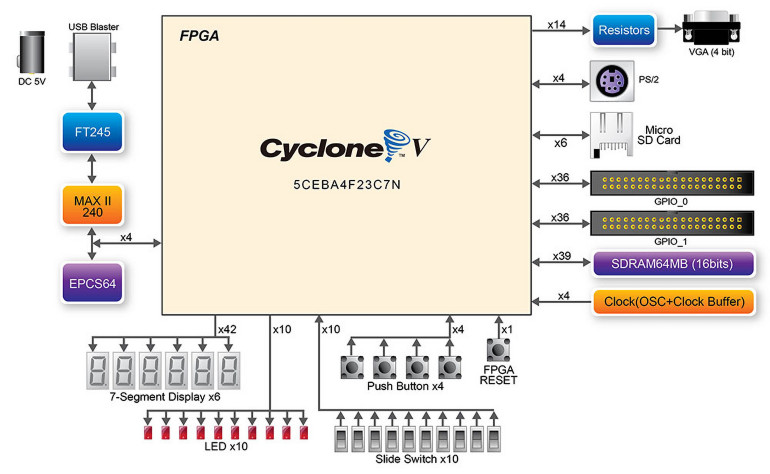

Powyższy produkt zawiera układ FPGA rodziny Cyclone V firmy Intel, którego pojemność wynosi 49 tys. konfigurowalnych bloków logicznych. Występują w nim takie peryferia jak: przyciski, diody LED, przełączniki, wyjście VGA oraz gniazdo PS/2, do którego można dołączyć m.in. klawiaturę, czy mysz. Konfiguracja zestawu odbywa się z zastosowaniem sterownika USB-Blaster i układu EPCS64. Zakres projektów: od bramek logicznych do kontrolerów, ograniczony tylko wyobraźnią twórcy. Przykłady: sterowanie silnikiem, karty video i urządzenia przenośne. Lecz nie tylko - może to być również prosta gra video z użyciem wyjścia VGA i pamięci SDRAM. A nawet projektor slajdów zapisanych na karcie microSD, którą można włożyć do dedykowanego gniazda. Krótko mówiąc DE0-CV to funkcjonalna platforma sprzętowa do tworzenia zaawansowanych aplikacji przy niskich kosztach. Jej rozmiary są nieduże (128×99 mm), podobnie jak waga (łatwo zatem przenosić zestaw).Napięcie zasilania płytki to 5 V.

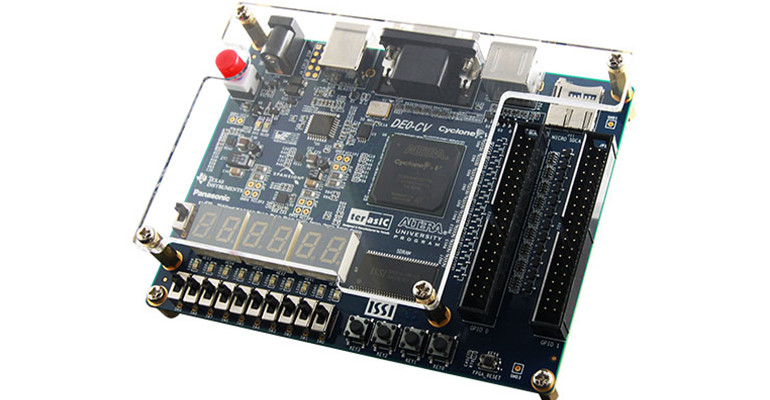

Wyrób jest chroniony przed upadkami dzięki pleksiglasowej pokrywie na górze.

Jego obsługę zapewnia środowisko Quartus firmy, wraz z dokumentacją elektroniczną na stronie producenta.

Do zestawu dołączono kabel USB i zasilacz zewnętrzny.

Produkt można kupić w sklepie AVT.

Specyfikacja zestawu DE0-CV:

- Układ FPGA rodziny Cyclone V:

- 49 tys. programowalnych bloków logicznych

- 3080 kbit pamięci RAM

- Pętle PLL - 4 szt.

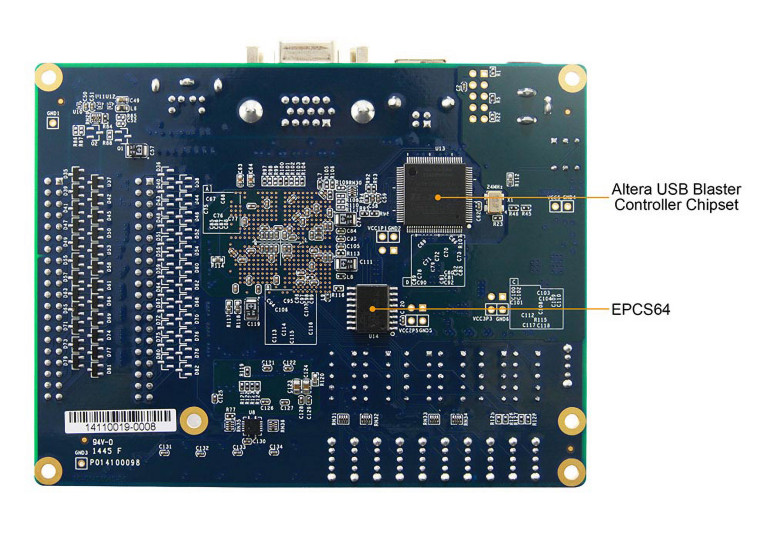

- Programowanie przez port USB, w oparciu o sterownik USB-Blaster lub w oparciu o układ EPCS64

- Pamięć SDRAM 64 MB o 16-bitowej magistrali danych

- Peryferia:

- Diody LED - 10 szt.

- Przełączniki - 10 szt.

- Przyciski użytkownika - 4 szt.

- Przycisk resetowania konfiguracji układu FPGA

- Sześciopozycyjny wyświetlacz siedmiosegmentowy

- 4-bitowe złącze VGA

- Gniazdo kart micro-SD

- Gniazdo PS/2

- Złącza GPIO 40 pinów - 2 szt.

- Zasilanie: z zewnątrz (5 V)

- Wymiary: 128×99 mm

Intel Quartus Prime Lite (narzędzie darmowe - zalecana wersja możliwe najnowsza, uwzględniająca rodzinę Cyclone V układów FPGA)