- moduł translatora poziomów logicznych zgodny z Grove,

- konwersja napięć 3,3 V – 5 V,

- wbudowane rezystory podciągające.

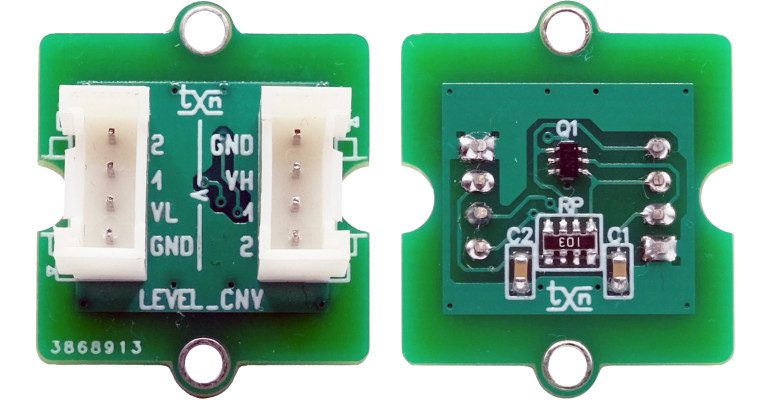

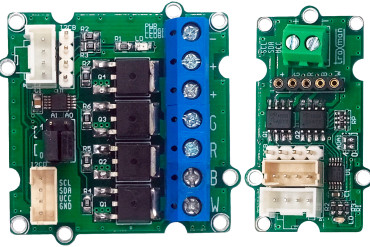

Aktywna część składa się z zaledwie dwóch elementów: podwójnego tranzystora Q1 typu BSS138 oraz drabinki rezystorowej RP. Kondensatory C1, C2 zapewniają dodatkowe odsprzęganie zasilania pomiędzy współpracującymi układami zewnętrznymi. Zasada działania została opisana w nocie aplikacyjnej AN10441 firmy NXP, dostępnej online.

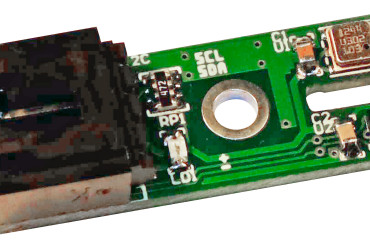

Magistrala I²C (zgodna z logiką o napięciu 3,3 V), wraz z napięciem zasilania, doprowadzona jest do translatora poprzez złącze LV. Interfejs 5-woltowy jest dostępny na złączu HV.

Jeżeli sygnały SCL i SDA przyjmują wysoki stan logiczny, obie struktury tranzystora Q1 są zatkane, a rezystory znajdujące się wewnątrz sieci rezystorowej RP podciągają sygnały magistral do odpowiednich poziomów logicznych. Jeżeli sygnał ze strony interfejsu 3,3 V (LV) przyjmuje stan niski, odpowiedni tranzystor otwiera się i „ściąga” swoim drenem sygnał interfejsu 5 V (HV) do masy. W przypadku, gdy stan niski pojawi się po stronie 5 V (HV), wewnętrzna dioda tranzystora Q1 wymusza stan niski (~0,7 V) po stronie interfejsu 3,3 V (LV), zaś – po przekroczeniu napięcia progowego bramka-źródło tranzystora Q1 – zostaje skutecznie zwarta poprzez obwód dren-źródło. Pomimo nieskomplikowanej konstrukcji układ doskonale sprawdza się przy konwersji dwukierunkowej, bez potrzeby zapewnienia dodatkowego sygnału sterującego przepływem danych. Jedynym ograniczeniem jest dopuszczalna prędkość transmisji – układ poprawnie pracuje do ok. 400 kHz. W przypadku magistrali I²C w trybie High Speed lub pracy przy jeszcze wyższych częstotliwościach, należy zastosować bardziej „złożony” konwerter, oparty na specjalizowanych układach scalonych.