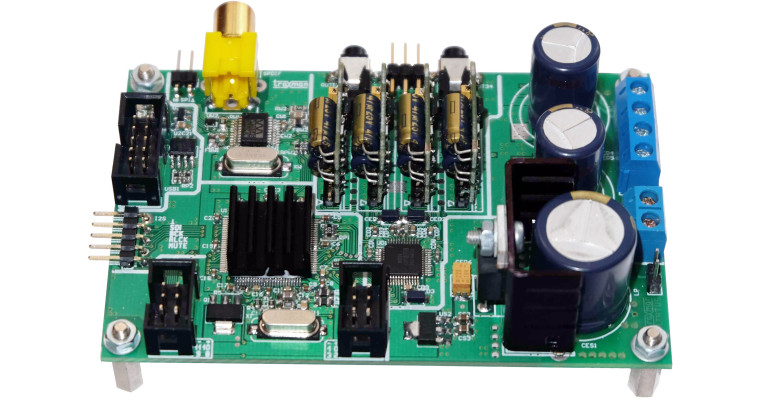

- Zbudowany na bazie procesora ADAU1442 z rodziny Sigma DSP firmy Analog Devices.

- Układ pracuje w trybie self boot, tzn. pobiera program z zewnętrznej pamięci EEPROM.

- Wejście w standardzie S/PDIF lub I²S.

- Częstotliwość próbkowania sygnału wejściowego z zakresu 32…192 kHz.

- Częstotliwość próbkowania sygnału wyjściowego 192 kHz.

- Zasilanie z zewnętrznego transformatora sieciowego 6 V AC/1 A + 2×12 V AC/0,5 A.

- Programowanie za pomocą Sigma Studio.

Zestaw MegaDSP+ bazuje na procesorze sygnałowym ADAU1442 (można też użyć ADAU1445) z rodziny Sigma DSP. Układ pracuje w trybie SELFBOOT, co oznacza, że po załączeniu zasilania lub restarcie pobiera program z zewnętrznej pamięci EEPROM. W tym trybie nie jest wymagany zewnętrzny procesor sterujący, a wszystkie zmiany konfiguracji lub parametrów wykonywane za pomocą interfejsu GPIO.

Moduł pracuje tylko z cyfrowym sygnałem wejściowym w standardzie S/PDIF (gniazdo „SPDIF”) lub I²S (gniazdo „I²S”). Dzięki wbudowanemu wielokanałowemu konwerterowi częstotliwości próbkowania jest możliwa współpraca ze źródłami sygnału o różnej częstotliwości próbkowania z przedziału 32…192 kHz. Wewnętrzna obróbka sygnału oraz przetwarzanie C/A odbywa się z częstotliwością 192 kHz.

Schemat ideowy Sigma DSP_Plus podzielono na bloki funkcjonalne. Sygnał wejściowy poprzez transformator separujący TW jest doprowadzony do odbiornika/dekodera UW1 typu WM8804. W zależności od potrzeb, jest możliwe doprowadzenie sygnału poprzez gniazdo SPDIF typu RCA lub przez SP1 w postaci listwy kołkowej. Układ WM8804 pracuje w typowej aplikacji, z własnym generatorem kwarcowym 12 MHz i konfiguracją sprzętową I²S/24-bity. Restart po załączeniu zasilania zapewnia U3 z bloku DSP. Dioda LCK sygnalizuje prawidłowy odbiór sygnału cyfrowego, a PWR obecność zasilania. Sygnał LCK wykorzystywany jest do wyciszania obwodów przetwornika C/A (bramka Schmitta UW2), gdy nie ma prawidłowego odbioru sygnału wejściowego S/PDIF.

Sygnał wejściowy I²S jest doprowadzony poprzez złącze I²S i połączony z portem szeregowym ADAU1442 (sygnały I²S: ISDI, ILRCK, IBCK). Podobnie jak w odbiorniku S/PDIF, jest możliwe zewnętrzne wyciszanie przetwornika C/A za pomocą sygnału IMUTE doprowadzonego do GPIO MP6.

Sygnał wyjściowy I²S (WSDI, WBLCK, WLRCK) o częstotliwości fs z zakresu 32…192 kHz jest doprowadzony do portu szeregowego I²S układu ADAU1442. Sygnał wyciszania WMUTE jest doprowadzony do GPIO MP6. Układ odbiornika S/PDIF uzupełniają elementy filtrujące zasilanie. Każdy z bloków funkcjonalnych układów UW1 jest zasilany poprzez filtr LC. Rezystor RP2 ogranicza przerost amplitudy szybkich sygnałów I²S.

Aplikacja procesora DSP1442 (U1) jest typowa, układ pracuje w trybie SELFBOOT. Parametry i program są przechowywane w pamięci EEPROM (U2). Zawartość pamięci jest programowana poprzez złącze USBI za pomocą programatora USBi. Układ ADM811T (U3) zapewnia poprawny restart układów po włączeniu zasilania. Procesor DSP jest taktowany za pomocą rezonatora kwarcowego o częstotliwości 12,288 MHz. Układ ma aktywny obwód generatora sygnałowego MCLK dla przetwornika C/A.

Blok DSP jest zasilany napięciem 3,3 V. Stabilizator z tranzystorem Q1 zapewnia zasilanie 1,8 V dla rdzenia procesora DSP. Poszczególne są zasilane poprzez odpowiednie filtry LC. Do złącza MP są doprowadzone cztery cyfrowe sygnały GPIO dla zewnętrznych przycisków lub układów sygnalizujących pracę DSP. Uwaga! GPIO ma niewielką obciążalność, więc do sterowania diodami LED należy użyć wzmacniaczy prądowych. Do złącza ADC są doprowadzone wejścia przetwornika A/C, które służą do przyłączenia potencjometrów przy „regulacji analogowej”. Każde złącze ma wyprowadzone zasilanie 3,3 V przeznaczone do zasilania zewnętrznych interfejsów GPIO. Dla rozproszenia traconej mocy procesor DSP jest wyposażony w niewielki radiator BGA.

Zamianą sygnału audio z cyfrowego na analogowy zajmuje się przetwornik PCM4104. W jego strukturze zaimplementowano 4 kanały przetwornika C/A (216 kHz/24 bity) oraz elastyczny interfejs szeregowy audio. W aplikacji MegaDSP+ układ PCM4104 jest konfigurowany sprzętowo za pomocą wejść FSx i FMTx. Sygnał audio nie jest przesyłany w standardzie I²S dopuszczającym transmisję tylko dwóch kanałów, ale w trybie TDM (Time Data Multiplexed), który upraszcza budowę interfejsu wielokanałowego przetwornika C/A, ponieważ sygnały wszystkich kanałów są multipleksowane czasowo i przesyłane tylko jedną linią danych.