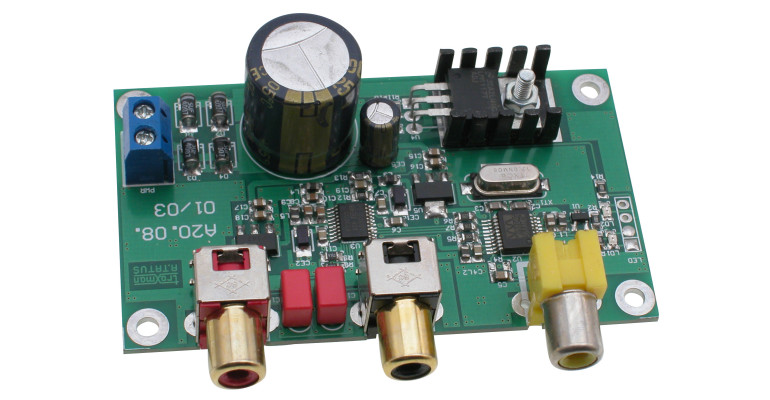

Sygnał wejściowy z gniazda S/PDIF jest doprowadzony do odbiornika U2 typu WM8804 pracującego w trybie konfiguracji sprzętowej master I²S z rozdzielczością 24 bitów. Dioda świecąca LD1 sygnalizuje odbiór ramki audio. Poprawne zerowanie odbiornika zapewnia U1 typu MCP100T. Aplikację WM8804 uzupełniają dwa filtry zasilania: dławik L1 i kondensator C1 dla obwodu PLL oraz dławik L2 i kondensator C4 dla części cyfrowej odbiornika.

Wyjściowy sygnał I²S jest doprowadzony do układu przetwornika U3 typu PCM5102A. Sygnał analogowy po odfiltrowaniu za pomocą obwodów RC złożonych z rezystorów R8i R9 oraz kondensatorów C12 i C13 jest podawany na gniazda RCA OUTL/OUTR. Obwód złożony z dławika L3 i kondensatorów CE1, C7 filtruje zasilanie części cyfrowej przetwornika. Kondensator C6 współpracuje z wewnętrznym stabilizatorem LDO, a dławik L4 i pojemność C10 filtrują zasilanie części analogowej.

Kondensatory C8 i C9 są elementami wbudowanej pompy ładunkowej wytwarzającej ujemne napięcie zasilania bloków analogowych.

Zwora FLT umożliwia wybór trybu pracy filtru: Normal Latency-FIR (zwarcie z GND) /Low Latency-IIR (zwarcie z V33D).

Układ PCM5102A ma możliwość wyciszania sygnału wyjściowego po podaniu na wejście XSMT napięcia mniejszego niż 2 V.

W modelu użyto tej funkcji do wyciszania wyjścia podczas załączania i wyłączania zasilania. Napięcie XSMT jest pobierane z dzielnika rezystancyjnego R13/R14.

Przetwornik jest zasilany z konwencjonalnego zasilacza liniowego, w którym jako wstępny regulator napięcia pracuje układ stabilizatora typu LM1117ADJ. Jego napięcie wyjściowe ustalono na 4,5 V. Układy niskoszumnych stabilizatorów U5 i U6 dostarczają zasilanie dla części cyfrowej i analogowej przetwornika. Dioda świecąca LD2 sygnalizuje załączenie zasilania. W zależności od potrzeb diody świecące LD1 i LD2 mogą zostać wlutowane bezpośrednio w płytkę lub za pomocą złącza LED sygnały sterujące mogą być wyprowadzone poza nią, np. na panel czołowy urządzenia. Przetwornik jest zasilany z niewielkiego transformatora toroidalnego 8 V AC (10 VA).