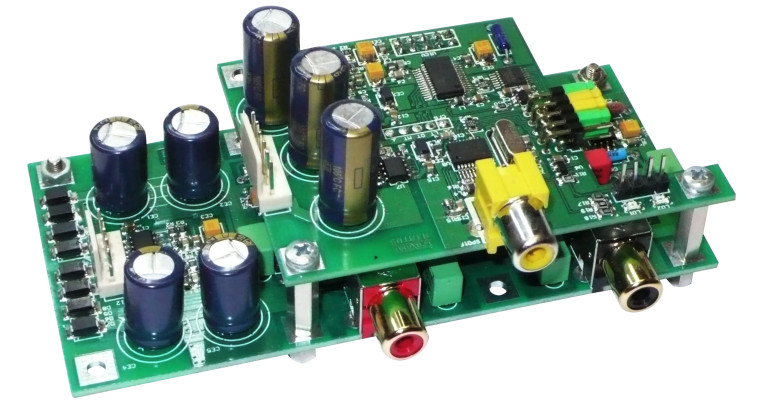

- Kultowy przetwornik AD1955 firmy Analog Devices.

- Zbudowany z dwóch płytek: analogowej i cyfrowej.

- Przetwarzanie sygnału w standardzie PCM i DSD.

- Akceptowane są sygnały o rozdzielczości 16, 18, 20 i 24 bitów.

- Częstotliwość próbkowania sygnału wejściowego: 32 kHz, 44,1 kHz, 48 kHz, 88,2 kHz, 96 kHz, 192 kHz.

- Wejście I²S.

- Dynamika sygnału wyjściowego przetwornika: 120 dB przy częstotliwości próbkowania 48 kHz.

- SNR: 123 dB, THD+N < -110 dB.

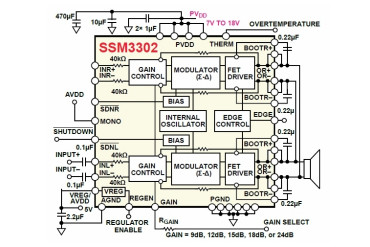

Układ AD1955 jest przystosowany do przetwarzania sygnałów w standardach PCM i DSD. W przedstawionym układzie jest wykorzystywany jest tylko I²S/PCM, jednak dla osób pragnących eksperymentować np. z konwerterami USB/PCM (DSD over PCM), sygnały sterujące AD1955 oraz wejście I²S zostały wyprowadzone na złącza zewnętrzne.

Cyfrowy sygnał wejściowy z gniazda S/PDIF jest doprowadzony do odbiornika U8 (WM8804) pracującego w trybie konfiguracji sprzętowej master I²S z rozdzielczością 24 bitów. Diody świecące LD1 i LD2 sygnalizują zasilanie i poprawny odbiór S/PDIF. Złącze LED umożliwia dołączenie diod LED zamontowanych np. na panelu frontowym obudowy. Układ U8 pracuje z kwarcem 12 MHz, dławiki i kondensatory filtrują napięcie zasilające poszczególne bloki funkcjonalne odbiornika.

Wyjściowe sygnały interfejsu S/PDIF (LRCKO, BCLKO, DATAO) i zegarowy MCLKO są doprowadzone do złącza USP. Podczas normalnej eksploatacji to złącze musi mieć założone zwory pomiędzy wyprowadzeniami 1-2, 3-4, 5-6, 7-8. Do złącza może być doprowadzony zewnętrzny sygnał I²S np. z konwertera USB/I²S, upsamplera i innych. Sygnały z gniazda USP wymagają zgodności z 3,3 V. Na złącze jest wyprowadzone też pomocnicze zasilanie 3,3 V/100 mA.

Sygnały interfejsu I²S ze złącza USP (LRCKI, BCLKI, DATAI, MCLKI) są doprowadzone do konwertera poziomów U2 (ADG3304), natomiast sygnał zegarowy MCLKI do konwertera z układem U5 (LVC1T45). Sygnały I²S wraz z sygnałem RES generowanym przez U6 (ADM811T) są zgodne z 5 V i doprowadzone do przetwornika U1 (AD1955). W modelu AD1955 pracuje z konfiguracją sprzętową. Umożliwia to dekodowanie sygnału PCM o częstotliwości próbkowania 96 kHz i rozdzielczości 24 bitów. Na złącze CFG są wyprowadzone sygnały interfejsu sterującego umożliwiającego zmianę ustawień oraz wykorzystanie wbudowanej regulacji głośności. Domyślnie należy zewrzeć wszystkie sygnały złącza CFG do masy za pomocą zwory SIP5. Rezystor konwersji R3 jest najważniejszym elementem układu i należy zadbać o zastosowanie komponentu o bardzo dobrej stabilności termicznej i odpowiedniej jakości. W prototypie użyto wyselekcjonowanego rezystora typu RN60 DALE. Podobnie rezystory obwodu polaryzacji R1, R2 powinny być o jak najwyższej jakości.

Wyjściowy sygnał prądowy z AD1955 oraz napięcie polaryzacji są doprowadzone do złącza UICV i stąd do modułu bloku analogowego. Moduł przetwornika C/A jest zasilany z niskoszumnego zasilacza LDO. Układ dostarcza trzech napięć, U3 – V50A zasilającego część analogową AD1955, U4 – V50D zasilającego część cyfrową AD1955 i konwertery poziomów U2,5 oraz U7 dostarczający napięcia V33D dla zasilania odbiornika SPDIF i pozostałych układów cyfrowych. Każdy ADP7102 zasilany jest z osobnego uzwojenia transformatora.

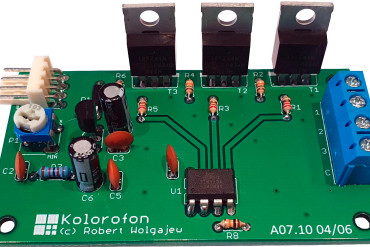

Współpracujące z ADP7102 dzielniki ustalają napięcia wyjściowe stabilizatorów. Możliwe jest zastosowanie układów o ustalonym napięciu wyjściowym +5 V i +3,3 V(przy zwartym R4 i niezamontowanych rezystorach R5 i R6, kondensatorze C8 i odpowiadających im komponentów w pozostałych zasilaczach). Blok analogowy zawierający konwertery I/U oraz dolnoprzepustowy filtr wyjściowy przedstawia rysunek 5. Różnicowy, prądowy sygnał analogowy ze złącza UICNV jest doprowadzony do konwerterów U/I z układami U1L oraz U2L. Po konwersji jest doprowadzony do filtra dolnoprzepustowego z układem U3L. Wyjściowy sygnał analogowy jest doprowadzony do złącza OUTL/R. W układzie zastosowano niskoszumne wzmacniacze operacyjne AD797. Podobnie jak w wypadku elementów R1…R3 przetwornika C/A wszystkie elementy bloku analogowego muszą być precyzyjne i o jak najwyższej jakości (np. DALE RN60), kondensatory powinny być o tolerancji co najwyżej 2%.