- Sygnałem wejściowy w standardzie S/PDIF.

- Możliwość pracy (bez zmian w układzie i oprogramowaniu) z sygnałami o fs z zakresu 32…96 kHz.

- Obróbka sygnału odbywa się z fs=96 kHz.

- Sygnał wyjściowy w formacie I²S, słowo 24-bitowe.

- Zasilanie z zewnętrznego transformatora 6…7,5 V AC o mocy minimalnej 4 VA.

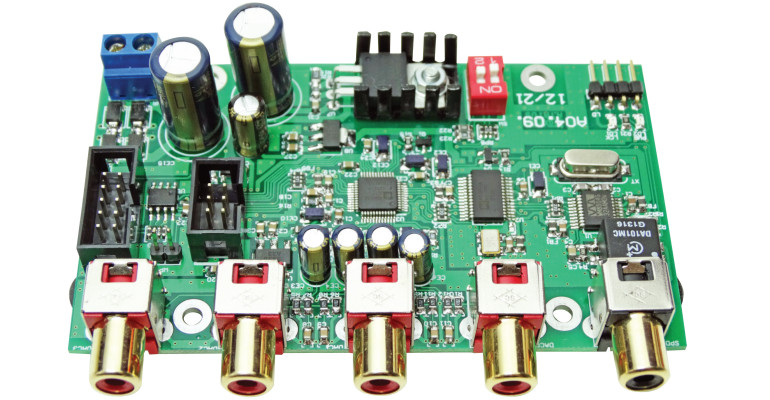

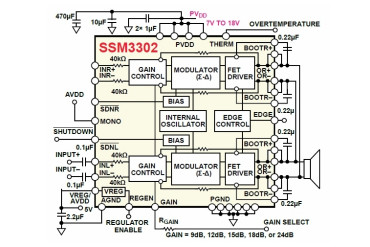

Moduł pracuje tylko z cyfrowym sygnałem wejściowym w standardzie S/PDIF. Dzięki zastosowaniu konwertera częstotliwości próbkowania, synchroniczny procesor sygnałowy ADAU1701 może bez zmian w układzie i oprogramowaniu pracować z sygnałami o fs z zakresu 32…96 kHz. Obróbka sygnału odbywa się z fs=96 kHz, co odpowiada maksymalnej obsługiwanej przez wbudowane przetworniki C/A częstotliwości próbkowania. Taka konfiguracja umożliwia wykorzystanie układu w charakterze zwrotnicy aktywnej, korektora charakterystyki przenoszenia itp.

Schemat ideowy Sigma DSP+ jest podzielony na bloki funkcjonalne. Wejściowy sygnał S/PDIF poprzez transformator separujący TR1 jest doprowadzony do odbiornika/dekodera U1 (WM8804). Układ pracuje w typowej aplikacji, z konfiguracją sprzętową I²S/24 bity. Dioda świecąca LD1 sygnalizuje prawidłowy odbiór sygnału cyfrowego, natomiast LD2 załączenie napięcia zasilającego. Sygnał wyjściowy I²S o częstotliwości fs z zakresu 32…96 kHz jest doprowadzony do U2 (AD1895) pełniącego rolę konwertera częstotliwości próbkowania. Ze względu na synchroniczną pracę DSP nie jest możliwe obrabianie sygnałów o różnych częstotliwościach fs bez zmian w układzie i oprogramowaniu, co ograniczałoby zastosowania modułu. Układ U2 (AD1895), przelicza próbki sygnału wejściowego o różnych częstotliwościach próbkowania na jedną fs=96 kHz, z którą pracuje DSP.

Układ AD1895 jest konfigurowany sprzętowo poprzez odpowiednie wymuszenie poziomów na doprowadzeniach konfiguracyjnych. Wyprowadzeniami SMIx jest ustalany format sygnału wejściowego – w prototypie jest to I²S (SMI2…0=001). Wejście BYPASS umożliwia pominięcie bloku ASRC (w prototypie jest on zawsze aktywny). Wyprowadzeniami SMO1/SMO0 jest ustalany format sygnału wyjściowego (I²S=01), natomiast WLOx – długość słowa wyjściowego (24 bity=00). Wejścia MMx ustawiają tryb master/slave i krotność częstotliwości próbkowania.

W modelu U4 jest skonfigurowany do pracy w trybie master – dla sygnału wyjściowego, przy krotności fs=256 (MMx=011).

Dla poprawnej pracy układu ASRC jest wymagany generator sygnału taktującego wykonany w oparciu o lokalny oscylator kwarcowy lub zewnętrzny generator. Maksymalna częstotliwość współpracującego generatora to 30 MHz. Dodatkowym wymogiem jest zapewnianie warunku fosc>138×fs. Zewnętrzny generator o częstotliwości 24,576 MHz spełnia ten warunek z zapasem dla fs=96 kHz będąc jednocześnie źródłem sygnału zegarowego dla ASRC i DSP.