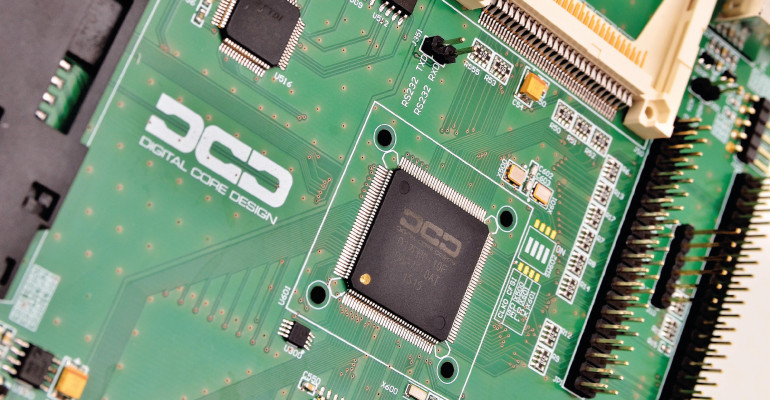

Najnowszy procesor D32PRO to nowoczesny układ RISC, 32-bitowy, oferowany jako IP Core (w modelu bez opłat, tzw. royalty-free). Jego wydajność została udowodniona w strukturze krzemowej (silicon proven) – układ wykonano w procesie technologicznym 110 nm. Procesor D32PRO ma zintegrowany koprocesor zmiennoprzecinkowy (FPC) oraz bogaty zestaw modułów peryferyjnych, jak np. USB, Ethernet, I²C, SPI, UART, CAN, LIN, RTC, HDLC, Smart Card etc. Dzięki temu pierwszy, polski, komercyjny procesor 32-bitowy stanowi atrakcyjną alternatywę dla dobrze znanych układów ARM Cortex M0/M0+/M1/M3, jak też i innych procesorów 32-bitowych oferowanych na rynku IP Core.

Architektura procesora D32PRO

D32PRO jest w pełni konfigurowalny. W zależności od potrzeb można wydatnie zmniejszyć powierzchnię zajmowaną przez procesor lub też zwiększyć jego wydajność. Z kolei dzięki zaawansowanej jednostce zarządzania energią (Power Management Unit), układ może być z powodzeniem zastosowany w aplikacjach energooszczędnych. W efekcie, zarówno typowe zastosowania, jak też i te związane z Internet of Things, Bluetooth Low Energy czy Wearables kreują szerokie spektrum zastosowań D32PRO.

Główną ideą przyświecającą inżynierom firmy DCD było zaprojektowanie procesora uniwersalnego i konfigurowalnego, nadającego się do zastosowania w różnorodnych aplikacjach. W D32PRO zaimplementowano autorską architekturę, która jest efektem optymalizacji maksymalnej częstotliwości zegara i opóźnienia w ścieżce danych. Dzięki temu zbudowano uniwersalny procesor, który doskonale radzi sobie z wykonywaniem kodu z wieloma skokami, jak też i kodu jednolitego, pokroju operacji arytmetycznych. Nie byłoby to możliwe bez zastosowania zmiennej architektury potokowej.

Kolejne innowacje widoczne w D32PRO można dostrzec w liście rozkazów. Bazuje ona na specjalnie zaprojektowanych instrukcjach, które są maksymalnie zbliżone w swoim działaniu do konstrukcji języka wyższego poziomu, jak np. C. W efekcie uzyskano bardzo dużą gęstość kodu, która jednocześnie idzie w parze ze zwartą i krótką listą rozkazów. Wśród nich można wymienić instrukcje pozwalające na optymalizację porównywania dwóch łańcuchów znaków czy też instrukcje znajdowania pierwszej jedynki w rejestrze.

Dla przykładu, można w tym miejscu wymienić instrukcję FZB pozwalającą na optymalizowanie wyszukiwania bajtów. W najprostszych procesorach 8-bitowych wyszukiwanie znaku NULL miało postać iterowania po wszystkich bajtach, na przykład:

size_t strlen(const char * str)

{

const char *s;

for (s = str; *s; s++);

return(s - str);

}W procesorach 32-bitowych zaczęto używać optymalizacji pozwalającej na jednoczesne sprawdzenie czterech bajtów rejestru:

D32PRO jest wyposażony w 13 rejestrów ogólnego przeznaczenia R0…R12, spośród których większość zapewnia automatyczną aktualizację zawartości po powrocie z przerwania. Dzięki tej czynności znacznie przyspieszono obsługę przerwań czy przełączanie kontekstu w systemach czasu rzeczywistego. Każdy ze wspomnianych rejestrów może być też użyty do operacji arytmetycznych, co jest o tyle przydatne, że jeśli odniesiemy to do klasycznego układu 8051 z łatwością zauważymy, że w pięćdziesiątkach jedynkach można było do tego wykorzystać tylko akumulator, co z kolei wiązało się koniecznością przeładowywania i zapisywania zawartości.

By jeszcze bardziej zwiększyć funkcjonalność procesora, wyposażono go w konfigurowalny układ przerwań zawierający 1 przerwanie niemaskowalne oraz do 32 przerwań maskowalnych. Sposób obsługi przerwania oraz jego detekcja są w pełni konfigurowane, dzięki czemu użytkownik może ustawić detekcję zbocza lub poziomu czy też konfigurować priorytety oraz sposób wejścia do obsługi przerwań.

Nowoczesne mikrokontrolery 32-bitowe powinny być projektowane ze szczególnym naciskiem na niski pobór energii. Nie inaczej rzecz ma się z D32PRO, który został wyposażony w zaawansowany system obniżania poboru energii. Moduł PMU (Power Management Unit) dynamicznie kontroluje częstotliwość zegara pozwalając na zaoszczędzenie energii w momencie, gdy nie jest wymagana maksymalna wydajność. W D32PRO można konfigurować podzielnik zegara procesora oraz osobno podzielnik zegara modułów peryferyjnych. Dzięki temu nic nie stoi na przeszkodzie, by wprowadzić wyłącznie sam rdzeń w tryb energooszczędny, gdy tymczasem wymagane peryferia będą śledzić otoczenie z nominalnym zegarem. Co więcej, sam rdzeń można także wprowadzić w tryb stop, w którym jest zatrzymywane taktowanie rdzenia, programując powrót do stanu normalnej pracy przez przerwanie od wybranych układów peryferyjnych. Procesor może także wyłączyć peryferia, które nie są używane w aplikacji, dzięki czemu można jeszcze bardziej zmniejszyć zapotrzebowanie na energię.