# **META-DX2+ Family**

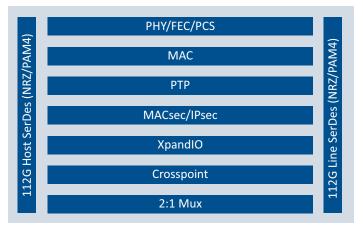

1.6T Ethernet MAC/PHYs Supporting MACsec/IPsec Encryption and Port Aggregation With Retimer, Gearbox, Hitless 2:1 Mux and Crosspoint

## Summary

The META-DX2+ family of devices are multi-purpose 1.6T Ethernet MAC/PHYs supporting rates from 1 GbE to 800 GbE and 112G PAM4 long reach SerDes. These versatile devices support encryption, port aggregation, Class C/D PTP and hitless 2:1 multiplexing, as well as SerDes crosspoint functionality that enables connectivity to a variety of optical modules, Direct Attach Copper (DAC) cables, packet processors and Ethernet switches.

Encryption is a key feature of META-DX2+, providing security via MACsec or IPsec at full line rate. MACsec encrypts Ethernet traffic at the frame level and supports "VLAN tag in the clear", enabling multi-hop routing of encrypted packets. IPsec encrypts IP packets which ensures security across wide-area networks. By providing encryption within META-DX2+, packet processors can offload the task of encryption to META-DX2+, enabling systems to scale up to larger bandwidths while providing end-to-end security.

The META-DX2+ family offers variants with 48 SerDes, enabling 1.6T gearbox or hitless 2:1 mux configurations, which is double the capacity of other solutions and cuts the device count in half to enable smaller form factors. The META-DX2+ 32 SerDes variants are pin compatible with the META-DX2L device, enabling META-DX2L designs to easily add encryption, port aggregation, or MAC layer services such as PTP, all within a single Software Development Kit (SDK).

## Highlights

- 1.6T gearbox and retimer configurations

- 1.6T hitless 2:1 mux for working/protect architectures

- Dual 800G ETC (Ethernet Technology Consortium), Quad 400 GbE and 16x 1/10/25/40/50/100 GbE MAC/PHYs

- Integrated 1.6T MACsec/IPsec encryption engines

- XpandIO enables port aggregation of low rate Ethernet clients over higher speed Ethernet interfaces

- Highly configurable crosspoint with ShiftlO, supporting multi-rate services on any port

- Supports Ethernet, OTN, Fibre Channel, and proprietary data rates for AI/ML applications

- PTP (IEEE 1588v2) support up to Class C/D

- 48 or 32 Long Reach (LR) capable 112G PAM4 SerDes

- Direct connectivity to passive copper cables including support for link training and auto-negotiation

- Industrial temperature range support, enabling deployments in outdoor environments

- Software Development Kit (SDK) that is common across the entire META-DX2 family, including all META-DX2+ and META-DX2L devices

- Support for Open Compute Project (OCP) based Switch Abstraction Interface (SAI) APIs

## META-DX2+ Block Diagram

## **Applications**

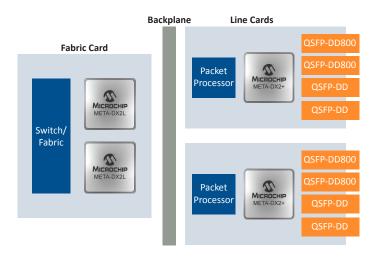

#### Switch/Router Applications

- Fabric card in a high-capacity modular system

- High-capacity line card in a modular system

- Fixed form factor switch

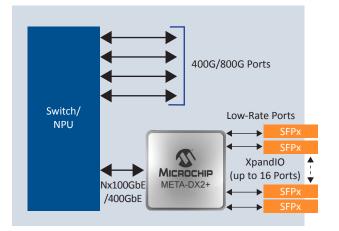

## Port Aggregation

- XpandIO aggregates multiple low-rate client ports, enabling efficient use of higher rate ports on the switch

- Allows client rates not supported by the Switch/NPU to be supported by the system

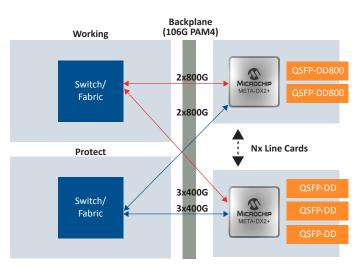

## Working/Protect Switch Using Hitless Mux

- Hitless switching between working and protect cards

- SerDes capable of driving across backplane or copper cables

## Compact Modular Transponders and Muxponders

- Crosspoint and gearbox functionality enable common hardware for QSFP28, QSFP-DD and QSFP-DD800 optics

- Supports Ethernet, OTN and Fibre Channel rates on a per-port basis

| META-DX2<br>Family Variant | Part # | Retimer /<br>Gearbox | Crosspoint   | ShiftIO      | Hitless<br>2:1 Mux | MACsec/<br>IPsec | XpandIO      | # of<br>SerDes | Max Capacity<br>(Retimer) | Max Capacity<br>(Gearbox) | Package<br>Size (mm) |

|----------------------------|--------|----------------------|--------------|--------------|--------------------|------------------|--------------|----------------|---------------------------|---------------------------|----------------------|

| META-DX2L                  | PM6200 | $\checkmark$         | $\checkmark$ |              | $\checkmark$       |                  |              | 32             | 1.6T                      | 800G                      | 23 x 30              |

| META-DX2+                  | PM6216 | $\checkmark$         | $\checkmark$ | $\checkmark$ | $\checkmark$       | $\checkmark$     |              | 32             | 1.6T                      | 800G                      | 23 x 30              |

|                            | PM6210 | $\checkmark$         | $\checkmark$ | $\checkmark$ | $\checkmark$       | $\checkmark$     | $\checkmark$ | 32             | 1.6T                      | 800G                      | 23 x 30              |

|                            | PM6214 | $\checkmark$         | $\checkmark$ | $\checkmark$ | $\checkmark$       |                  |              | 48             | 1.6T                      | 1.6T                      | 33 x 33              |

|                            | PM6218 | $\checkmark$         | $\checkmark$ | $\checkmark$ | $\checkmark$       | $\checkmark$     |              | 48             | 1.6T                      | 1.6T                      | 33 x 33              |

The Microchip name and logo and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies. © 2022, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved. 9/22 DS0004033A